インテルのみ表示可能 — GUID: qzk1506351718681

Ixiasoft

インテルのみ表示可能 — GUID: qzk1506351718681

Ixiasoft

1.4.1. 必須AFU CSRの定義

AFUのCSRに対するソフトウェア・アクセスには、次の要件が定義されています。

- ソフトウェアは、アライメントされたクワッドワード (8バイト) として64ビットのCSRにアクセスすることが想定されています。64ビット・レジスターのフィールド (ビットまたはバイト) の変更には、クワッドワード全体が読み出され、適切なフィールドが変更され、クワッドワード全体が書き戻されます (リードモディファイライト動作)。

- 32ビットのCSRをサポートするAFUの場合も同様に、ソフトウェアは、アライメントされたダブルワード (4バイト) でそれらにアクセスすることが想定されています。

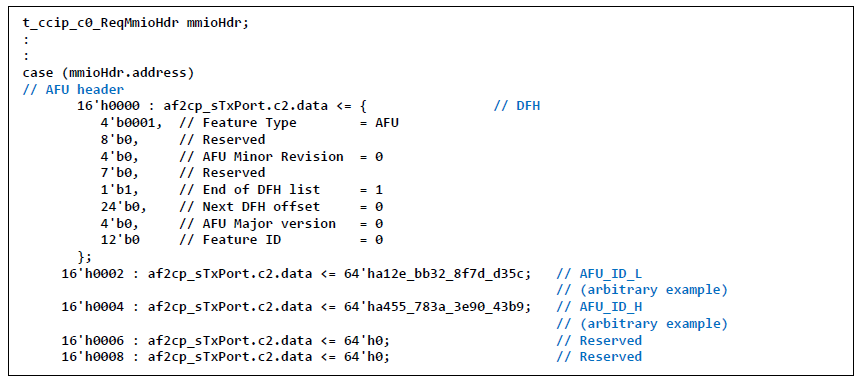

CCI-Pに準拠するAFUにはそれぞれ、次の表で定義されている4つの必須レジスター (0x0000のDEV_FEATURE_HDR (DFH) を除く) の実装が必要です。これらのレジスターを実装していない場合、もしくは正しく実装していない場合、AFUの検出に失敗する、もしくは他の予期せぬ動作が起こる場合があります。

| 属性 | 展開 | 説明 |

|---|---|---|

| RO | Read Only | ビットはハードウェアでのみ設定されます。ソフトウェアはこのビットの読み出しのみ可能です。書き込みには効果がありません。 |

| Rsvd | Reserved | 今後定義される内容に予約されています。AFUはこれらを0に設定する必要があります。ソフトウェアは、これらのフィールドを無視する必要があります。 |

| 名称 | DWORDアドレス オフセット (CCI-P) |

バイト・アドレス・ オフセット (ソフトウェア) |

|---|---|---|

| DEV_FEATURE_HDR (DFH)

ビットの説明に関しては、表 43 を参照ください。

注: AFU のCSRは64ビットです。

|

0x0000 | 0x0000 |

| AFU_ID_L AFU_ID GUIDの下位64ビット |

0x0002 | 0x0008 |

| AFU_ID_H AFU_ID GUIDの上位64ビット |

0x0004 | 0x0010 |

| DFH_RSVD0 | 0x0006 | 0x0018 |

| DFH_RSVD1 | 0x0008 | 0x0020 |

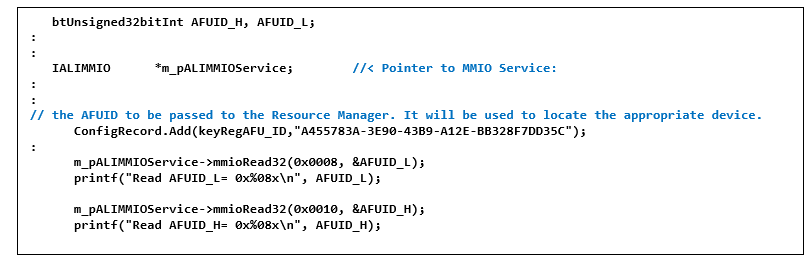

ソフトウェアとAFU RTLは同じAFU IDを参照する必要があります。

| ビット | 属性 | デフォルト | 説明 |

|---|---|---|---|

| 63:60 | RO | 0x1 | タイプ: AFU |

| 59:52 | Rsvd | 0x0 | 予約済み |

| 51:48 | RO | 0x0 | AFUマイナーバージョン番号 ユーザー定義の値 |

| 47:41 | Rsvd | 0x0 | 予約済み |

| 40 | RO | 該当なし | リストの末尾 1’b0: この後に別のフィーチャー・ヘッダーがあります (「次のDFHのバイトオフセット」を確認ください。) 1’b1: これはこのAFUの最後のフィーチャー・ヘッダーです。 |

| 39:16 | RO | 0x0 | 次のデバイス・フィーチャー・ヘッダーへのバイトオフセットです。つまり、現在のアドレスからのオフセットです。 DFHのバイトオフセット例に関しては、表 45 を参照ください。 |

| 15:12 | RO | 0x0 | AFUメジャーバージョン番号 ユーザー定義の値 |

| 11:0 | RO | 該当なし | CCI-Pバージョン番号 ccip_if_pkg.svのCCIP_VERSION_NUMBERパラメーターを使用します。 |