インテルのみ表示可能 — GUID: led1440196960710

Ixiasoft

2.1. デザイン問題の分析のためにNetlist Viewersを使用する場合

2.2. Netlist Viewersによる インテル® Quartus® Primeデザインフロー

2.3. RTL Viewerの概要

2.4. Technology Map Viewerの概要

2.5. Netlist Viewerのユーザー・インターフェイス

2.6. 回路図

2.7. ソース・デザイン・ファイルと他の インテル® Quartus® Primeウィンドウのクロスプローブの実行

2.8. 他の インテル® Quartus® Primeウィンドウからのビューワのプロービング

2.9. タイミング・パスの表示

2.10. Design Netlistの改訂履歴の最適化

2.6.1. 複数タブ表示での回路図の表示

2.6.2. 回路図シンボル

2.6.3. スケマティック・ビューで項目の選択

2.6.4. スケマティック・ビューのショートカット・メニュー・コマンド

2.6.5. スケマティック・ビューでのフィルタリング

2.6.6. スケマティック・ビューでのノードの内容の表示

2.6.7. スケマティック・ビューでノードの移動

2.6.8. Technology Map ViewerでのLUT表現の表示

2.6.9. ズーム・コントロール

2.6.10. Bird's Eye Viewでナビゲートする

2.6.11. ページへのスケマティックの分割

2.6.12. スケマティック・ページでのネットのフォロー

2.6.13. リソース・プロパティー・ビューアでの選択の維持

4.2.3.1. ガイドライン:ソースコードを最適化する

4.2.3.2. ガイドライン:スピードではなく、面積に対して合成を最適化する

4.2.3.3. ガイドライン:マルチプレクサーの再構築

4.2.3.4. ガイドライン:Balanced設定またはArea設定でWYSIWYGプリミティブ再合成を実行する

4.2.3.5. ガイドライン:レジスターパッキングを使用する

4.2.3.6. ガイドライン:Fitter Constraintsを削除する

4.2.3.7. 合成中の階層のフラット化

4.2.3.8. ガイドライン:メモリーブロックのターゲット変更

4.2.3.9. ガイドライン:面積を削減するための物理合成オプションの使用

4.2.3.10. ガイドライン:DSPブロックのリターゲットまたはバランス

4.2.3.11. ガイドライン:より大きなデバイスを使用する

5.6.5.1. ソース・コードの最適化

5.6.5.2. レジスター間のタイミング改善のまとめ

5.6.5.3. フィジカル・シンセシスの最適化

5.6.5.4. エクストラ・フォート消費電力最適化の設定をオフにする

5.6.5.5. エリアではなくスピードへの合成の最適化

5.6.5.6. 合成中の階層のフラット化

5.6.5.7. シンセシス・エフォートをHighへ設定する

5.6.5.8. ファンアウトを制御するためのロジックの複製

5.6.5.9. シフト・レジスターの推論の防止

5.6.5.10. 合成ツール内で使用可能な他の合成オプションを使用する

5.6.5.11. Fitterシード

5.6.5.12. 最大ルータタイミング最適化レベルを設定する

6.1.3.1. アーキテクチャー固有のデザイン情報の表示

6.1.3.2. デバイスで使用可能なクロックネットワークの表示

6.1.3.3. クロックセクター使用率の表示

6.1.3.4. ルーティングの輻輳の表示

6.1.3.5. I/Oバンクの表示

6.1.3.6. Viewing High-Speed Serial Interfaces (HSSI)

6.1.3.7. 配置したノードの送信元と送信先の表示

6.1.3.8. 配置されたリソースのファンインおよびファンアウト接続の表示

6.1.3.9. 隣接したファンインおよびファンアウト接続の生成

6.1.3.10. 選択したコンテンツの表示

6.3.1. Chip PlannerでのLogic Lock領域間の接続の表示

6.3.2. Logic Lockの領域

6.3.3. Logic Lockの領域の属性

6.3.4. インテル® Quartus® Primeスタンダード・エディションと インテル® Quartus® Primeプロ・エディション間の割り当ての移行

6.3.5. Logic Lock領域の作成

6.3.6. Logic Lock領域の形状のカスタマイズ

6.3.7. Logic Lock領域へのデバイスリソースの配置

6.3.8. 領域の階層化

6.3.9. トランシーバーの追加機能

6.3.10. Logic Lock Regionsウィンドウ

6.3.11. リージョンへのスナップ

インテルのみ表示可能 — GUID: led1440196960710

Ixiasoft

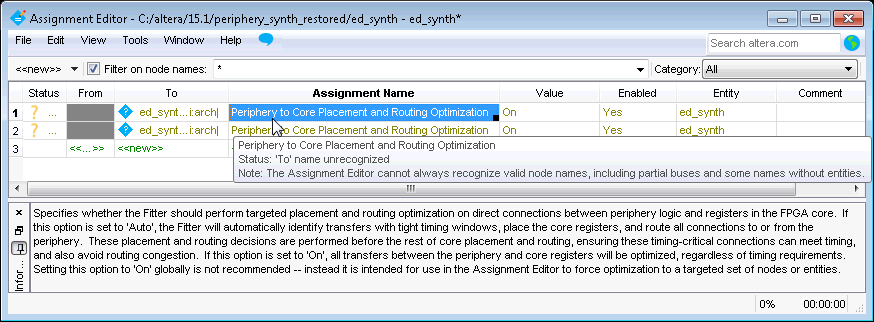

5.7.2. Assignment EditorでCore OptimizationsをPeripheryに設定する

Assignment EditorでPeriphery to Core Placement and Routing Optimization(P2C/C2P)設定をオンにすると、 インテル® Quartus® Primeソフトウェアはデザイン内の選択したインスタンスに対して、ペリフェラルからコアへ、またはコアからペリフェラルへの最適化を実行します。

オプションで、Advanced Fitter Settingsダイアログボックスの設定を使用して、インスタンス別にコアからコアへの最適化を実行できます。

- インテル® Quartus® Primeソフトウェアで、Assignments > Assignment Editorをクリックします。

- 選択したパスのAssignment Nameカラムをダブルクリックし、ドロップ・ダウン・リストのPeriphery to core register placement and routing optimizationオプションをクリックします。

- Toカラムで、最適化するP2C/C2Pパス上のペリフェラル・ノードまたはコア・レジスター・ノードを選択します。 Fromカラムを空のままにします。

Assignments Editorにパスを表示するには、まずデザインに対してAnalysis&Synthesisを実行する必要があります。