インテルのみ表示可能 — GUID: aif1597700885121

Ixiasoft

インテルのみ表示可能 — GUID: aif1597700885121

Ixiasoft

6.3.3. ユーザーロジックからHBM2 Controller AXI Interfaceへのタイミングの改善

Controller Backpressure Latency

Controller Backpressure Latency機能を使用すると、ユーザー・インターフェイスによるコントローラーのREADY信号 (アドレス書き込み、アドレス読み出しおよび書き込みチャネル) へのインターフェイス接続が柔軟になります。この機能をイネーブルにすると、HBM2コントローラーによって提供されるREADY信号の発行は、指定した値に従って早くなります。

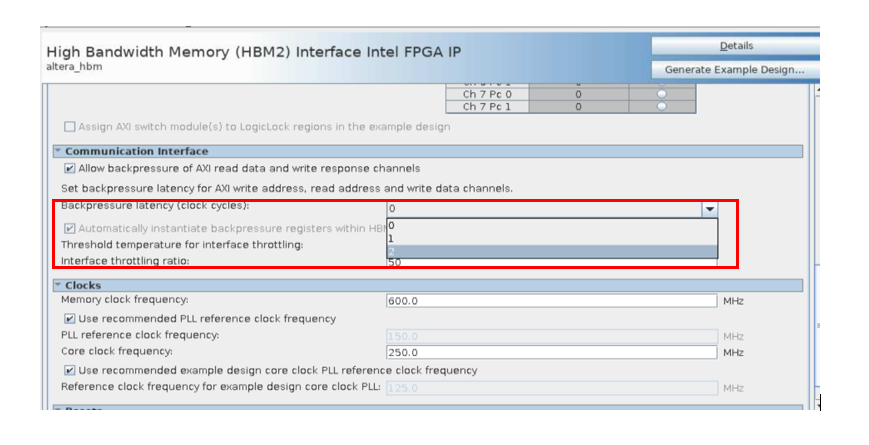

デフォルトでは、この機能はディスエーブルです。バックプレッシャー・レイテンシーは0クロックサイクルです。この機能をイネーブルにした場合、目標バックプレッシャー・レイテンシーは、1または2クロックサイクルに指定します。HBM2コントローラーで提供するREADY信号であるAXI Write Address Ready (AXI_X_Y_AWREADY)、AXI Read Address Ready (AXI_X_Y_ARREADY)、およびAXI Write Data Ready (AXI_X_Y_WREADY) の発行は、指定したサイクル数だけ早くなります。

この機能をイネーブルにした場合、N サイクル (N に対してサポートされているクロックサイクル値は、機能がイネーブルの場合は1、2、ディスエーブルの場合は0) を設定すると、HBM2 Controllerで提供するREADY信号 (つまりAXI Write Address Ready (AXI_X_Y_AWREADY)、AXI Read Address Ready (AXI_X_Y_ARREADY)、およびAXI Write Data Ready (AXI_X_Y_WREADY) の発行は、N クロックサイクルだけ早くなります。Controller Backpressure Latencyのイネーブルの対象は、選択したHBM2インターフェイスに対するすべてのAXIインターフェイスにわたります。

ゼロ以外のバックプレッシャー・レジスター値を選択する場合、レジスターステージの追加を選択できます。次のいずれかの方法で行います。

- HBM2 IPを使用して、AXIインターフェイスのソフト・ロジック・アダプターにレジスターを追加することができます。これはデフォルトの動作です。

- AXIインターフェイスのタイミング (早期READYデアサート) を手動で処理するには、Automatically instantiate back pressure registers within HBM2 IP オプションをディスエーブルします。

AXI Backpressure Latencyの使用

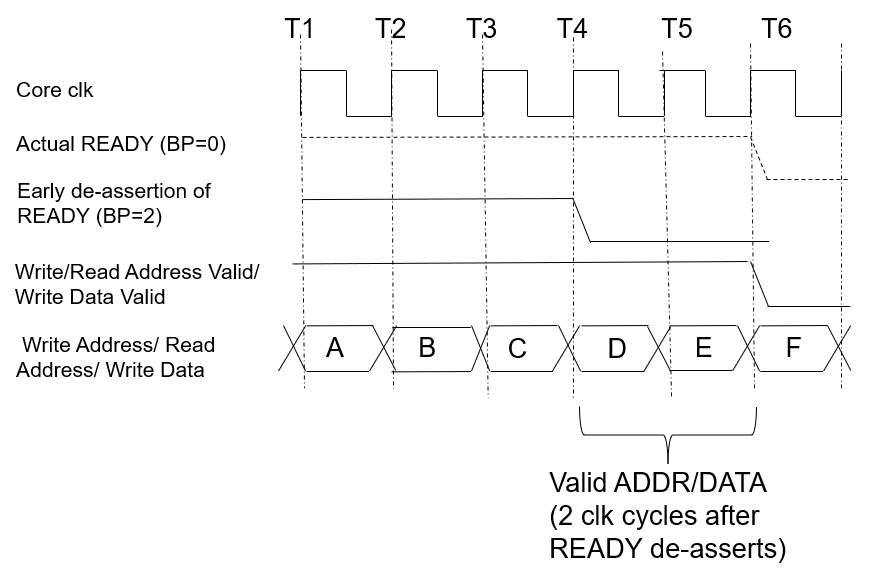

次のタイミング図で示しているバックプレッシャー・レイテンシーは、2クロックサイクルです。この値によって、READY信号のデアサートの発生は、それ以外の場合よりも2コア・クロックサイクル早くなります。バックプレッシャー・レイテンシーが2クロックサイクルの場合、ユーザー・インターフェイスに2クロックサイクルが追加され、READYデアサートに応答します。そのために、有効なWrite Address/Write DataおよびRead Addressを継続してREADYデアサート後に2クロックサイクルの間提供します。

次の図に示すように、2クロックサイクルのバックプレッシャー・レイテンシーによって、READYがクロックサイクルT4でデアサートされます。ただし、HBM2コントローラーでは、引き続き入力の受け入れをクロックサイクルT4およびT5 (入力DおよびE) で行います。これは、対応するVALID信号がアクティブである場合です。

早期READY信号を使用したタイミング・クロージャーの促進

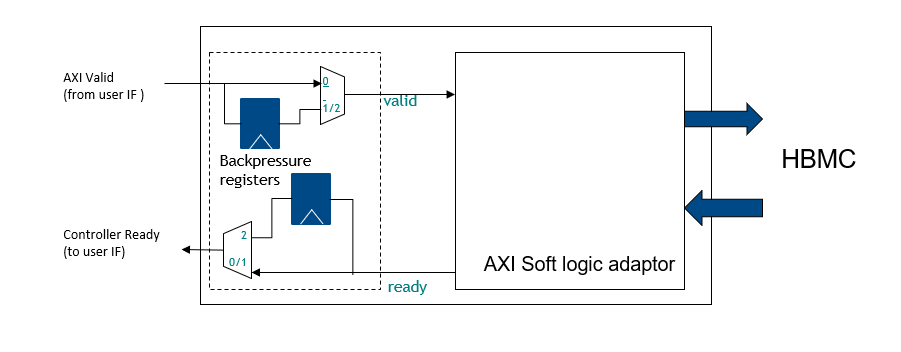

N の非ゼロAXIバックプレッシャー・レイテンシーを指定した場合、合計 N 個のパイプライン・レジスターを、HBM2コントローラーからのAXIインターフェイス出力およびREADY入力に追加することができます。追加されるパイプライン・レジスターの合計がInputとOutputの両方向で N になるようにすると、タイミング・クロージャーが容易になります。HBM2 IPをイネーブルして、HBM2 IPパラメーター・エディターからこれらのレジスターを生成します。

インテル® Quartus® Prime開発ソフトウェア・バージョン19.4以降では、HBM2 IPにより、次のレジスターがBackpressure latencyの設定に基いて追加されます。レジスターを手動で挿入する必要はなくなりました。

- Backpressure latencyが1に設定されている場合、コントローラーによるREADY信号のデアサートは、1クロックサイクル早くなります。レジスターステージが1つ、コアからHBM2コントローラーへのAXI Interface Validパス内の信号に追加されます。

- Backpressure latencyが2に設定されている場合、コントローラーによるREADY信号のデアサートは、2クロックサイクル早くなります。HBM2 IPにより、次のレジスターが追加されます。

- レジスターステージが1つ、AXI Interface Validおよびユーザーロジックからの関連するAXIインターフェイス信号に追加されます。

- レジスターステージが1つ、コントローラーからコアへのREADY信号 (AWREADY、WREADY、ARREADY) に追加されます。

次の図で示すバックプレッシャー・レジスターは、ユーザー・コア・ロジックとAXIソフト・ロジック・アダプター間のデータパスに配置されています。これにより、タイミング・クロージャーが容易になります。

Write応答とReadデータ・インターフェイスのタイミング

読み出しおよび書き込み応答バックプレッシャー機能をイネーブルした場合でも、Write応答およびReadデータ・インターフェイスのタイミングの処理は、ゼロ・サイクル・レイテンシーで行ってください。ユーザー・インターフェイスで発行したBREADYおよびRREADYをHIGHに駆動して、コントローラーによる出力の提供が、該当する場合にできるようにしてください。

読み出しおよび書き込み応答バックプレッシャー機能をディスエーブルすると、パイプライン・レジスターを読み出しおよび書き込み応答出力に追加できます。これは、BREADYおよびRREADYは常にHIGHであり、ユーザー・インターフェイスでは応答の受け入れ準備が常時可能であることを示しているからです。