インテルのみ表示可能 — GUID: ocl1513363708013

Ixiasoft

インテルのみ表示可能 — GUID: ocl1513363708013

Ixiasoft

6.3.1. AXI書き込みトランザクション

AXI書き込みアドレス

AXI書き込みトランザクションを開始するには、有効なWrite Address信号の発行を、AXI Write Address Busである AWADDR で行います。ユーザーロジックでは、有効な書き込みアドレスの提供を AWADDR バスで行い、AWVALID をアサートして、アドレスが有効であることを示す必要があります。マスターで AWVALID 信号をアサートできるのは、有効なアドレスおよび制御情報を駆動している場合のみです。

HBM2コントローラーでは、Writeコマンド・トランザクションの受け入れ準備ができると、AWREADY 信号をアサートします。アドレス転送が起こるのは、AWVALID と AWREADY の両方がアサートされた場合です。

自動プリチャージのユーザー信号である AWUSER もまた、AWADDRと同じタイミングに従います。つまり、AWUSER の提示は AWADDR と同じタイミングでする必要があります。

AXI書き込みデータ

書き込みバースト中、マスターで WVALID 信号をアサートするのは、マスターで有効な書き込みデータを駆動している場合のみです。アサートされた場合、WVALID のアサート状態を保つ必要があるのは、スレーブで WREADY をアサートした後のクロックの立ち上がりエッジまでです。マスターによる WLAST 信号のアサートは、最終書き込み転送のバーストでの駆動中に行う必要があります。ユーザーロジックによる書き込みアドレスの発行は、書き込みデータの発行と同じ順序で行う必要があります。書き込みデータ転送が起こるのは、WVALIDとWREADYの両方がHIGHのときです。

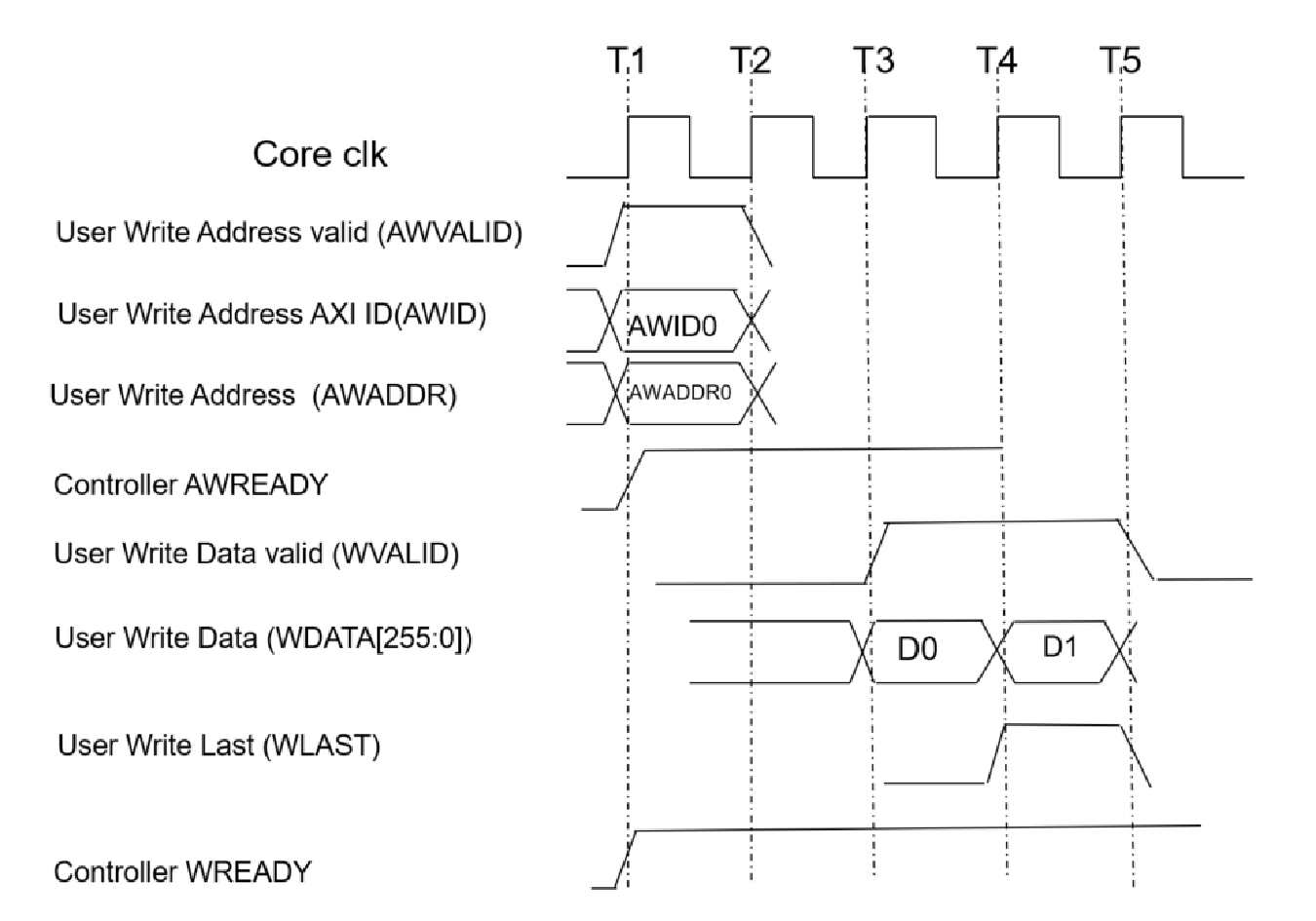

次の図で示しているのは、BL8 Writeトランザクションです。マスターでは、T1でのWriteアドレス (WA0) のアサートをトランザクションID AWID0 を使用して行います。HBM2コントローラーで AWREADY をアサートするのは、書き込み要求の受け入れ準備ができたときです。マスターでは、WriteデータのアサートをクロックサイクルT3で行います。コントローラー WREADY はすでにアサートされているため、書き込みデータの受け入れ開始は、サイクルT3からです。バースト8トランザクションの最後の部分がアサートされるのは、クロックサイクルT4です。

書き込み応答チャネル

HBM2コントローラーでは、Write Responseチャネルを使用して、正常なWriteトランザクションに応答します。スレーブで BVALID 信号をアサートするのは、スレーブで有効な書き込み応答を駆動している場合のみです。アサートされた場合、BVALID のアサート状態を保つ必要があるのは、マスターで BREADY をアサートした後のクロックの立ち上がりエッジまでです。BREADY のデフォルト状態がHighになる可能性があるのは、マスターによる1サイクルでの書き込み応答の受け入れが常時可能な場合のみです。