インテルのみ表示可能 — GUID: tdk1513364114047

Ixiasoft

インテルのみ表示可能 — GUID: tdk1513364114047

Ixiasoft

6.3.2. AXI読み出しトランザクション

読み出しアドレス

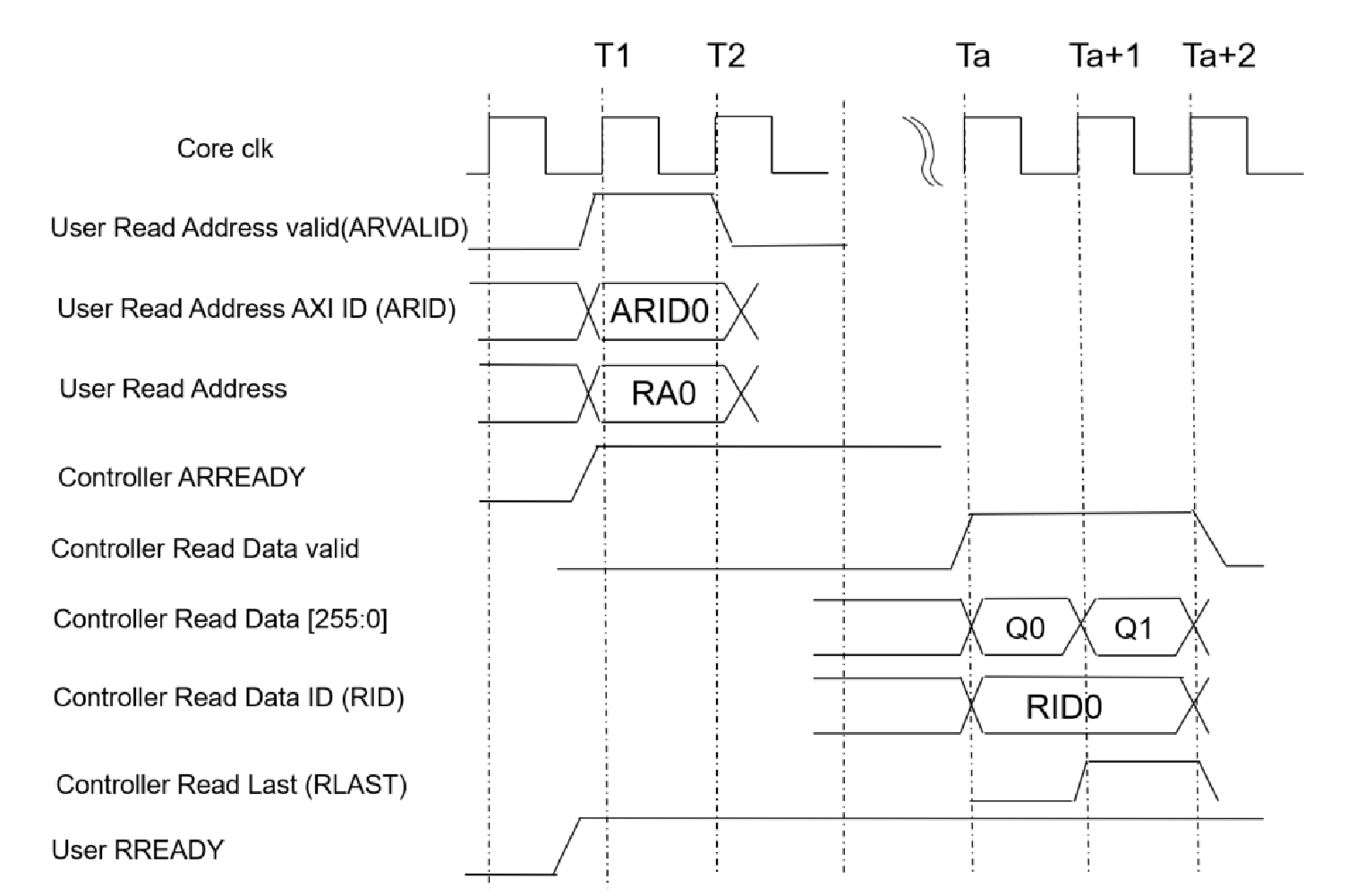

ユーザーロジックで ARVALID 信号をアサートするのは、有効なReadアドレスである ARADDR 情報を駆動している場合のみです。アサートされた場合、ARVALID をアサート状態に保つ必要があるのは、HBM2コントローラーで ARREADY 信号をアサートした後のクロックの立ち上がりエッジまでです。ARREADY がHighの場合、HBM2コントローラーでは、提示された有効なアドレスを受け入れます。キャリブレーションが完了し、HBM2 Controllerでコマンド受け入れ準備ができると、ARREADY がHighにアサートされます。自動プリチャージのユーザー信号である ARUSER も ARADDR と同じタイミングに従います。つまり、ARUSER の提示は ARADDR と同じタイミングで行う必要があります。

読み出しデータチャネル

HBM2コントローラーで、RVALID 信号をアサートするのは、HBM2コントローラーで有効な読み出しデータをユーザーロジックに駆動している場合です。マスター・インターフェイスでは、RREADY 信号を使用して、データを受け入れることを示します。マスターで、HBM2コントローラーからの読み出しデータの受け入れが常時可能な場合、RREADY の状態は、常にHighに保持できます。ソフトロジックの先入れ先出し (FIFO) バッファーのインスタンス化にHBM2パラメーター・エディターを使用できるのは、HBM2コントローラーで RREADY 信号のデアサートが予想される場合です。HBM2コントローラーで RLAST 信号をアサートするのは、バースト内の最終読み出し転送を駆動しているときです。

次の図で示しているのは、BL8読み出しトランザクションです。ユーザーロジックでは、読み出しアドレス (RA0) のT1でのアサートをトランザクションID ARID0 を使用して行います。HBM2コントローラー ARREADY は既にアサートされており、READコマンドは受け入れられます。コントローラーでは、ユーザー・インターフェイスに読み出しデータを返します。これは、READコマンドをHBM2 DRAMに対して発行した後です。HBM2コントローラーでは、ReadデータのアサートをクロックサイクルTBで行います。ReadトランザクションID (RID) は、HBM2コントローラーによって提供される場合は、Read Address ID (ARID) に対応します。バースト8トランザクションの最後の部分 (RLAST) のアサートは、クロックサイクルTa+1で行われます。