インテルのみ表示可能 — GUID: hig1507663331843

Ixiasoft

1.2.2.1.1. Device Selection セクション

1.2.2.1.2. Power Rail Data and Configuration セクション

1.2.2.1.3. VRM Data セクション

1.2.2.1.4. Rail Group Summary セクション

1.2.2.1.5. VRM Impedance セクション

1.2.2.1.6. BGA Via セクション

1.2.2.1.7. Plane セクション

1.2.2.1.8. Spreading セクション

1.2.2.1.9. スプリットプレーンの実装

1.2.2.1.10. FEFFECTIVE セクション

1.2.2.1.11. Decoupling セクション

1.2.2.1.12. Results Summary セクション

1.2.2.1.13. System_Decap タブを使用したFPGA システムのデカップリングの導出に推奨されるフロー

インテルのみ表示可能 — GUID: hig1507663331843

Ixiasoft

1.3.4. より良い精度のためのさらなる最適化

プレレイアウトにおける最適化で説明した2 つの方法は、デカップリング・ソリューションの大まかな見積もりのために主にプレレイアウト段階で使用されますが、ここで説明する方法は、より正確で最適化された見積もりを得る方法を示しています。

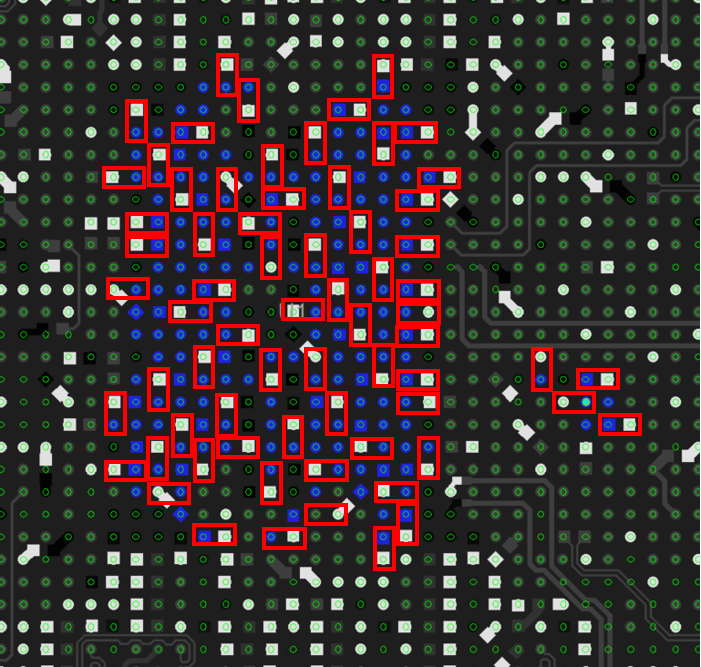

コンデンサー・モデルの確認では、デカップリング・コンデンサー・ライブラリーが実際のモデルで更新され、デキャップ数の最適化では、マニュアルモードでのデキャップ数が制御される一方で、この方法は、推定プロセスからスプレッディングR およびL を除外する方法を示します。以下の図に示すように、FPGA の反対側のデキャップの実装には機械的制限はなく、赤いボックスは、直接配置できるデキャップの0402 の70ea を示します。合計124ea のデキャップの大部分はBGA の直下に実装できます。したがって、この場合、スプレッディング・オプションは無視できます。

図 37. FPGA の反対側におけるデキャップの実装

- Feffective オプションをCalculate からOverride に変更します。

- 数値が同じであるかどうかを確認します。

- 数値が変更された場合は、次の例で推奨される10.18 MHz のFEFFECTIVE を白い空白にライトします。

図 38. FEFFECTIVE のオーバーライド

- Spreading オプションをLow からIgnore に変更します。

スプレッディング・オプションが無視されると、ZPDN 全体が少し下がり、マージンが増えます。図 39. スプレッディングを無視する

- デキャップ数の最適化に示すように、各コンデンサーに対してマニュアル最適化を繰り返します。

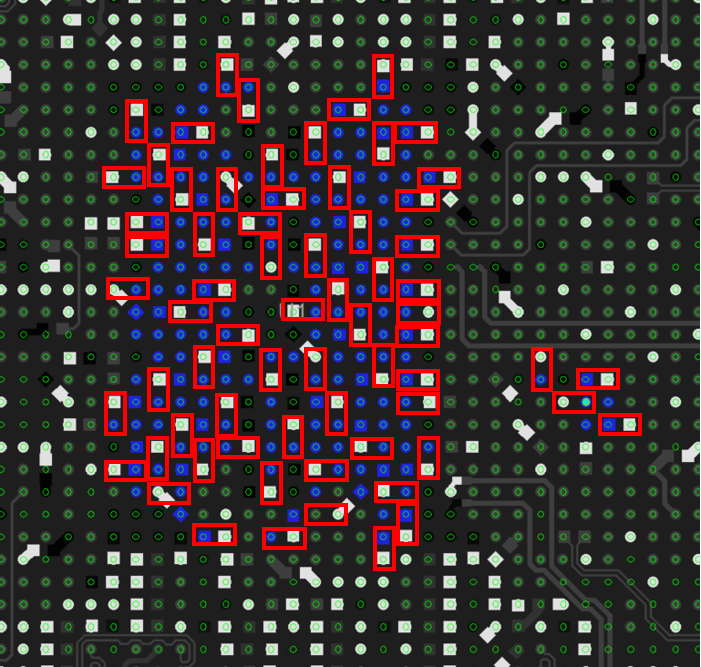

最適化プロセスの後、0402 のコンデンサー (下の表で赤い枠で囲んだもの) のうち48ea だけが見積もられ、0402 のコンデンサーの総許容数は70ea です。また、この例では、残りの大きいコンデンサー (下の表で青い枠で囲んだもの) をBGA 領域に配置することができます。最終結果は以下の通りです。最適化プロセスの第1 および第2 ラウンドを通じて、コンデンサーの総数が、バルク・コンデンサーを含む301ea の上限から、77ea まで減少しました。注: PDN ツールの結果にはすでに、VRM 用のバルク・コンデンサー・ソリューションが含まれています。しかし、インテルでは、PDN ツールの見積りが要件を満たすことができるかどうかを確認するために、VRM ベンダーに必要な出力キャパシタンスについて問い合わせることを推奨しています。VRM ライブラリーのEnpirion モデルには、すでに必要な出力キャパシタンスが含まれています。必要なコンデンサーの組み合わせについては、各VRM モデルのデータシートを参照してください。図 40. マニュアルでのデカップリング結果の要約:最適化後、ラウンド2