インテルのみ表示可能 — GUID: kmg1551188082851

Ixiasoft

1. Intel Agilex® 7 FシリーズおよびIシリーズ汎用I/Oの概要

2. Intel Agilex® 7 FシリーズおよびIシリーズのGPIOバンク

3. Intel Agilex® 7 FシリーズおよびIシリーズのHPS I/Oバンク

4. Intel Agilex® 7 FシリーズおよびIシリーズのSDM I/Oバンク

5. Intel Agilex® 7 FシリーズおよびIシリーズI/Oトラブルシューティングのガイドライン

6. Intel Agilex® 7 FシリーズおよびIシリーズ汎用I/OのIP

7. プログラマブルI/O機能の説明

8. Intel Agilex® 7汎用I/Oユーザーガイド: FシリーズおよびIシリーズに関連するドキュメント

9. Intel Agilex® 7汎用I/Oユーザーガイド: FシリーズおよびIシリーズの改訂履歴

2.5.1. VREFソースと VREF ピン

2.5.2. VCCIO_PIO電圧に基づくI/O規格の実装

2.5.3. OCTキャリブレーション・ブロック要件

2.5.4. I/Oピンの配置要件

2.5.5. I/O規格の選択とI/Oバンク供給の互換性チェック

2.5.6. 同時スイッチング・ノイズ

2.5.7. 特別なピンの要件

2.5.8. 外部メモリー・インターフェイスのピン配置要件

2.5.9. HPS共有I/Oの要件

2.5.10. クロッキング要件

2.5.11. SDM共有I/Oの要件

2.5.12. 未使用ピン

2.5.13. 未使用のGPIOバンクの電圧設定

2.5.14. 電源シーケンス中のGPIOピン

2.5.15. GPIO入力ピンのドライブ強度の要件

2.5.16. 最大DC電流制限

2.5.17. 1.2 V I/Oインターフェイスの電圧レベルの互換性

2.5.18. Avalon® Streamingインターフェイス・コンフィグレーション・スキームのGPIOピン

2.5.19. I/Oレーンあたりの最大真の差動信号のレシーバーペア

インテルのみ表示可能 — GUID: kmg1551188082851

Ixiasoft

2.5.8. 外部メモリー・インターフェイスのピン配置要件

External Memory Interfaceのグループ化にピンを選択する場合、同じグループ内のすべてのピンを隣接するサブバンクに配置する必要があります。

GPIOバンク内では、上部のサブバンクはダイのエッジ付近に配置されており、下部のサブバンクはFPGAコア付近にあります。

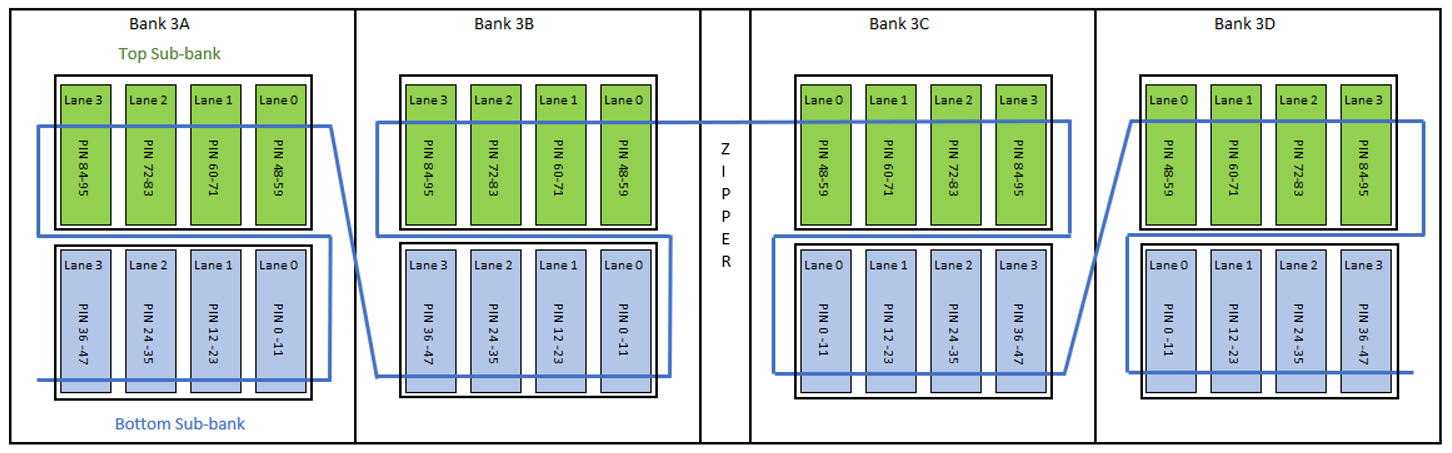

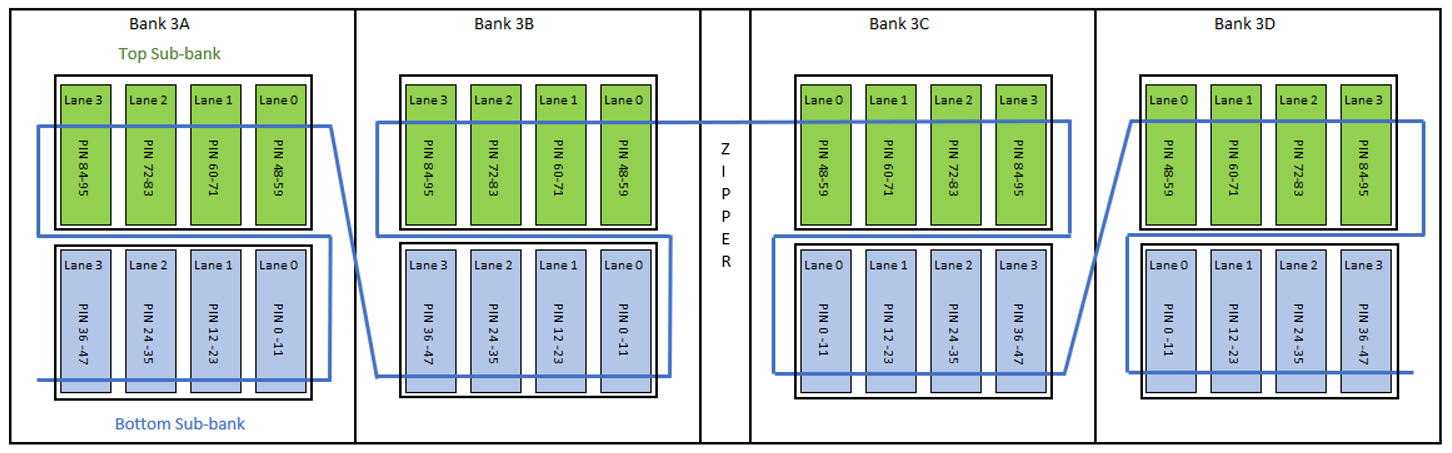

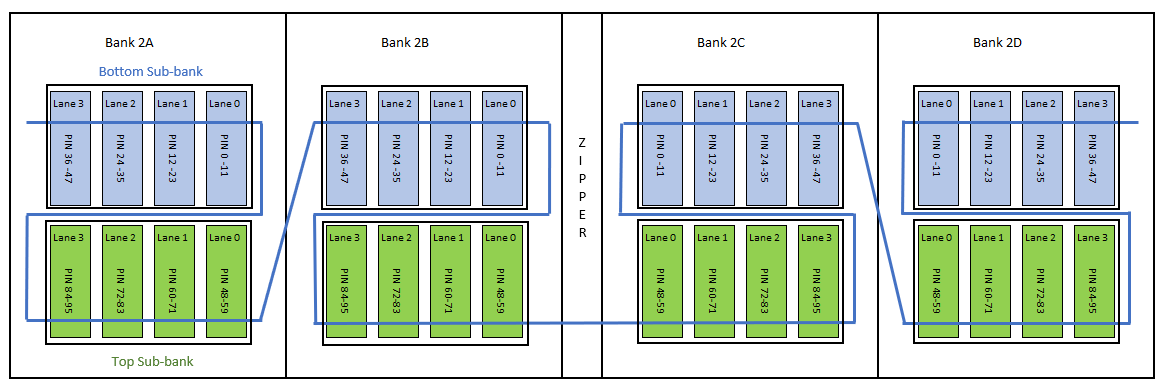

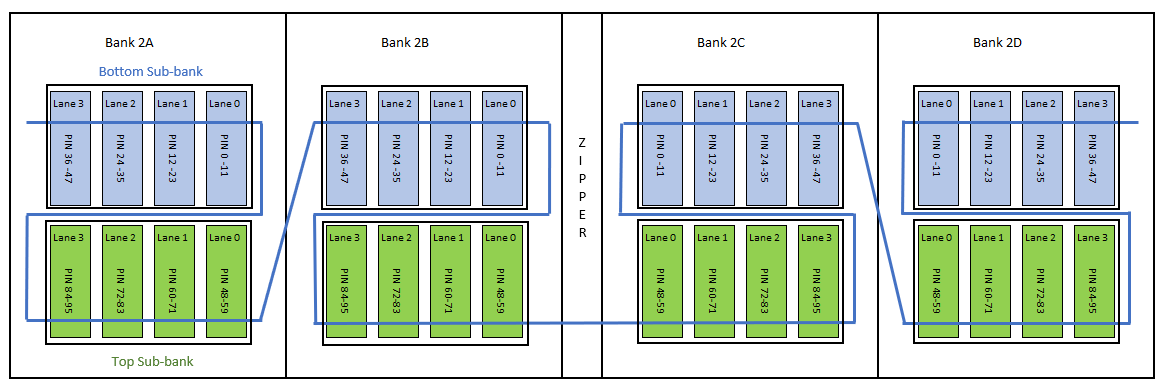

サブバンク間の相互接続により、サブバンクが1列にチェーンされます。次の図では、さまざまなサブバンクのI/Oレーンをチェーンして、さまざまなデバイスバリアントの上部と下部のI/O行を形成する方法例について示しています。これらの図は、デバイスパッケージの裏面図に対応するシリコンダイのトップビューを表しています。

図 18. AGF 012デバイスとAGF 014デバイスの上部GPIO行のサブバンク順序

図 19. AGF 012デバイスとAGF 014デバイスの下部GPIO行のサブバンク順序

I/Oバンク内の2つのサブバンクは、いずれかのサブバンクがボンティングされていないか、部分的にボンティングされていない限り、互いに隣接しています。図中の青い線は、サブバンク間の接続を示しています。

例えば、AGF 012デバイスとAGF 014デバイスの上部列のバンクでは、

- バンク3Aの上部サブバンクは、バンク3Aの下部サブバンクとバンク3Bの下部サブバンクに隣接しています。

- バンク3Bの上部サブバンクは、バンク3Bの下部サブバンクとバンク3Cの上部サブバンクに隣接しています。

- バンク3Bの上部サブバンクは、2つのサブバンクの間にジッパーブロックがある場合でも、バンク3Cの上部サブバンクに隣接しています。

- バンク3Bの上部サブバンクは、バンク3Aの下部サブバンクに隣接していません。

デバイスのピンアウトファイルのIndex within I/O Bank値に基づいて、I/Oバンク内のピンの位置を識別できます。