インテルのみ表示可能 — GUID: pad1526350748341

Ixiasoft

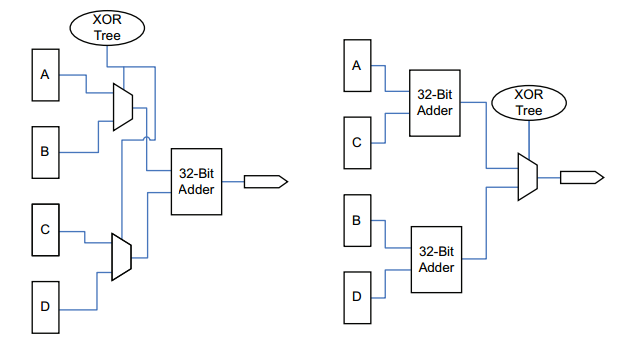

2.5.9. グリッチ低減に向けたパイプライン・ロジック

カスケード接続された論理ブロックの長いチェーンでは、入力信号間のパス遅延の差によりグリッチが発生する可能性があります。フリップフロップを挿入しこれらの長いチェーンを切断することで、連続するロジックセルへのグリッチの伝播を防ぎます。

XIO機能を多用する回路 (巡回冗長検査など) は、カスケード接続すると大幅にグリッチする傾向があります。パイプライン・レジスターを追加するか、アーキテクチャーを見直し信号のトグルを削減します。

グリッチ傾向のあるデザイン

関連情報