インテルのみ表示可能 — GUID: xop1633471022804

Ixiasoft

インテルのみ表示可能 — GUID: xop1633471022804

Ixiasoft

10.1.4.2. ツールキットパラメーター

Toolkitパラメーター/ウィンドウには、次のサブタブがあります。

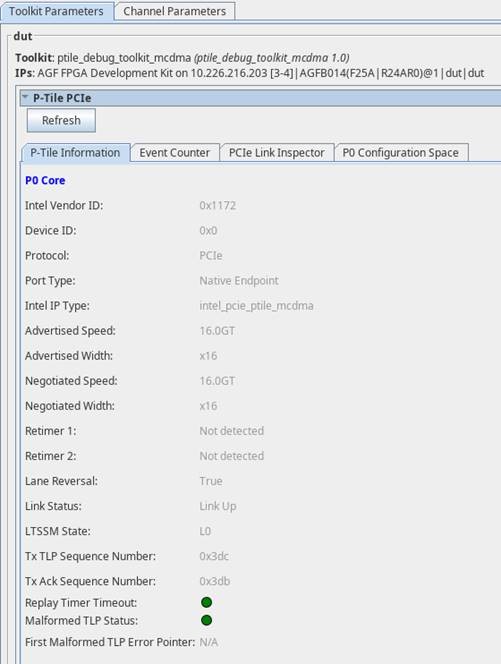

Rタイルの情報

これは、初期化時にFタイルのデバッグ・ツールキットによって読み取られた、IPが生成されたときのPCIeIPパラメーター・エディターでのFタイルPCIeIPパラメーター設定の要約を一覧表示します。デザインでポート分岐を有効にしている場合(たとえば、x8x8)、このタブには各コア(P0コア、P1コアなど)のFタイル情報が入力されます。

すべての情報は読み出し専用です。

Refreshボタンをクリックして設定を読み出します。

| パラメーター | 値 | 説明 |

|---|---|---|

| インテルベンダーID | 1172 | IP Parameter Editorで設定したベンダーIDを示します。 |

| Device ID | 0 | これは、ベンダーによって割り当てられたデバイスの一意の識別子です。 |

| Protocol | PCIe | プロトコルを示します。 |

| Port Type | ルートポート、エンドポイント 1 | ハードIPポートタイプを示します。 |

| PHYの IPタイプ | intel_pcie_mcdma | 使用するIPタイプを示します。 |

| アドバタイズされた速度 | 8.0GT、16.0GT | アドバタイズされた速度を示します。これは、IP Parameter Editorで設定したものです。 |

| アドバタイズされた幅 | x16、x8、x4 | アドバタイズされた幅を示します。これは、IP Parameter Editorでコンフィグレーションしたものです。 |

| 交渉速度 | 2.5GT, 5.0GT, 8.0GT, 16.0GT | リンクトレーニング中のネゴシエートされた速度を示します。 |

| 交渉幅 | x16/x8/x4/x2/x1 | リンクトレーニング中にネゴシエートされたリンク幅を示します。 |

| リンクステータス | リンクアップ、リンクダウン | リンク(DL)がアップしているかどうかを示します。 |

| LTSSMステート | Revision History for the F-Tile Avalon Streaming Intel FPGA IP for PCI Express User Guide | リンクの現在のステートを示します。 |

| 車線反転 | True、False | リンクでレーン反転が発生するかどうかを示します。 |

| Retimer 1 | Detected、Not Detected | ルートポートとエンドポイントの間でリタイマーが検出されたかどうかを示します。 |

| Retimer 2 | Detected、Not Detected | ルートポートとエンドポイントの間でリタイマーが検出されたかどうかを示します。 |

| TxTLPシーケンス番号 | 16進数値 | 送信TLPの次の送信シーケンス番号を示します。 |

| TxAckシーケンスタイムアウト | 16進数値 | ACK/NAK DLLPの受信によって更新されるACKシーケンス番号を示します。 |

| リプレイタイマータイムアウト | 緑、赤 | 緑:タイムアウトなし 赤:タイムアウト |

| 不正な形式のTLPステータス | 緑、赤 | 緑:奇形のTLPなし 赤:不正な形式のTLPが検出されました |

| 最初の不正な形式のTLPエラーポインタ |

|

|

| PIPE PhyStatus (For F-Tile debug toolkit only) |

0.1 |

Indicates the PMA and PCS are in reset mode.

|

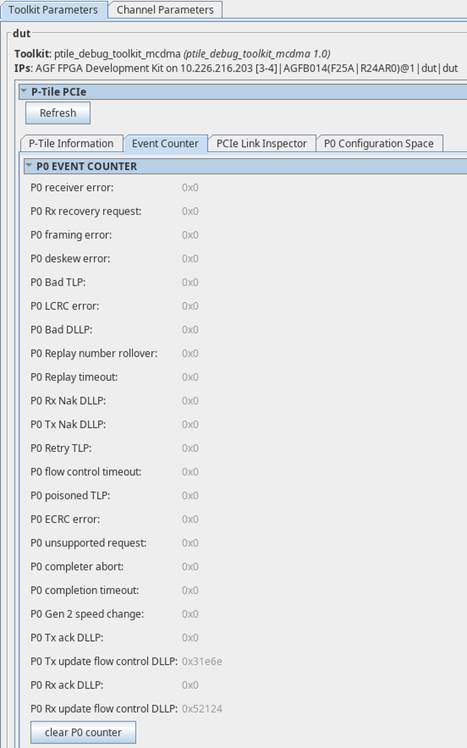

イベント・カウンタ

このタブでは、各ポートのレシーバーエラーの数、フレーミングエラーなどのエラーイベントを読み出すことができます。使用することができます P0カウンターをクリア/P1カウンターをクリア エラーカウンタをリセットします。

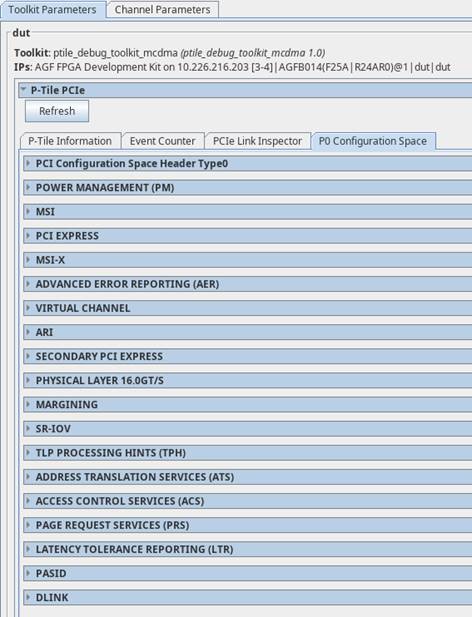

P0、P1コンフィギュレーション・デバイス

このタブでは、そのポートのコンフィグレーション・スペースレジスターを読み出すことができます。各ポートのコンフィグレーション・スペースを示す個別のタブが表示されます。