インテルのみ表示可能 — GUID: zjw1695945943639

Ixiasoft

インテルのみ表示可能 — GUID: zjw1695945943639

Ixiasoft

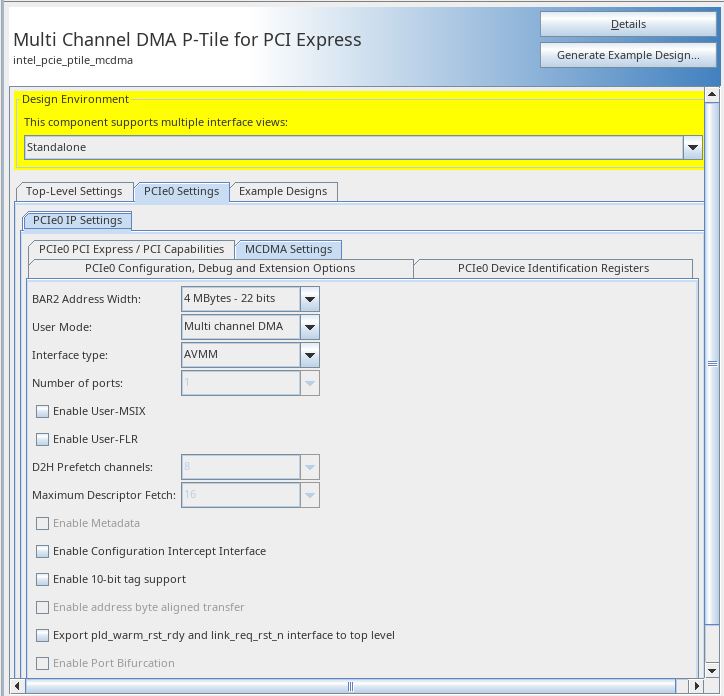

6.2.5. MCDMAの設定

| パラメーター | 値 | デフォルト値 | Description |

|---|---|---|---|

| BAR2アドレス領域 |

128 Bytes – 8 EBytes |

4 MBytes - 22 bits |

Address width for PIO AVMM port. Default address width is 22 bits |

| ユーザーモード |

8チャネルDMA バースト-MM Master Bursting Slave BAM+BAS BAM+MCDMA BAM+BAS+MCDMA Data Mover Mode only |

8チャネルDMA |

This option allows user to configure the mode of operation for MCDMA IP. MCDMA mode has the DMA functionality. BAM and BAS offer Bursting Master and Slave AVMM capabilities without DMA functionality

注: In R-Tile 4x4, Port 2 and 3 only support BAM, BAS and BAM+BAS user mode.

|

| インターフェイスの種類機能 |

AVMM AVST |

AVMM |

User logic interface type for D2HDM and H2DDM. Avalon-MM Interface |

| Number of ports |

1 |

1 |

Number of ports for AVMM and AVST interface is 1. |

| Enable User-MSIX |

ON、OFF |

Off |

User MSI-X is enables user application to initiate interrupts through MCDMA, this option is available only if the user selects MCDMA mode |

| Enable User-FLR |

ON、OFF |

Off |

User FLR, interface allows passing of FLR signals to the user side application |

| D2H Prefetch channels |

8 16 32 64 128 256 |

8 |

Sets the D2H Prefetch channels In the current release, the D2H Prefetch Channels parameter follows the total number of DMA channels that you select in the IP Parameter Editor up to 256 total channels. When the total number of channels selected is greater than 256, then D2H Prefetch channels are automatically fixed to 64.

注: This parameter applicable to AVST 1 port interface only.

|

| Maximum Descriptor Fetch |

16 32 64 |

16 |

Sets the maximum descriptors that are fetched per D2H prefetch channel.

注: This parameter is applicable to AVST 1 port interface only.

|

| Enable Metadata |

ON、OFF |

Off |

Enables Metadata

注: This parameter is only available when the Interface Type is set to AVST.

|

| Enable Configuration Intercept Interface |

ON、OFF |

Off |

Enable Configuration Intercept Interface |

| Enable 10-bit tag support interface |

ON、OFF |

Off |

This parameter is available for the following user modes: MCDMA, Bursting Slave, BAM+BAS, BAM+MCDMA and BAM+BAS+MCDMA

注: This parameter is not supported for R-tile. 10-bit tag is set to On by the IP.

|

| Enable address byte aligned transfer |

ON、OFF |

Off |

This is the option to enable the Byte aligned address mode support needed for Kernel or DPDK drivers and DMA makes no assumption on the alignment of data w.r.t to address.

注: This parameter is only available when the Interface Type is set to AVST.

|

| MSI Capability |

ON、OFF |

Off |

PCIe0のMSI機能を有効または無効にします。

注: This parameter is only available when User Mode is set to BAS or BAM+BAS.

|

| PF0 MSI 64-bit Addressing |

ON、OFF |

Off |

Enables or disables 64-bit MSI addressing. |

| 要求されたMSIメッセージの数 |

1 2 4 8 16 32 |

1 |

アプリケーション層がリクエストできるメッセージの数を指定します。Message Control レジスターの複数メッセージ対応フィールドの値を設定します。 |

| PF0 MSI Extended Data Capable |

ON、OFF |

Off |

PF0のMSI拡張データ機能を有効または無効にします。 |

| Export pld_warm_rst_rdy and link_req_rst_n interface to top level |

ON、OFF |

Off |

Exports pld_warm_rst_rdy and link_req_rst_n interface to top level.

注: This parameter is not available in R-Tile MCDMA IP.

|

| パラメーター | 値 | デフォルト値 | Description |

|---|---|---|---|

| Enable ATT |

ON、OFF |

Off |

Enables ATT for BAS |

| ATT Table Address Width |

1 - 9 |

3 |

Sets depth of ATT. Depth is equal to 2 to the power of number entered. |

| ATT Window Address Width |

10 - 63 |

16 |

Sets the number of BAS address bits to be used directly. |