インテルのみ表示可能 — GUID: nik1412379634062

Ixiasoft

2.1.1. Link Designerモジュールでの通信リンクの構築

2.1.2. Link and Simulation Setting

2.1.3. トランスミッターの設定

2.1.4. レシーバーの設定

2.1.5. IBIS-AMIラッパー

2.1.6. チャネル設定

2.1.7. バッチ・チャネル・シミュレーションのコンフィグレーション

2.1.8. クロストーク・アグレッサー・トランスミッターの設定

2.1.9. リピーターとリタイマーのコンフィグレーション

2.1.10. ノイズソースのリンク・コンポーネント

2.1.11. System Options

2.1.12. プロジェクト・マネージメントの機能

2.1.13. プロジェクトのアーカイブと解凍

2.1.14. Device Model Importer

2.1.15. 解析機能および事前シミュレーションと事前解析チェックリスト

2.1.16. COM解析

インテルのみ表示可能 — GUID: nik1412379634062

Ixiasoft

3. チュートリアル: PCI Express* 8GT

このチュートリアルでは、Advanced Link Analyzerを使用してリンク・シミュレーションを実行します。この例とそれに関連するチャネルモデルは、Advanced Link Analyzerディストリビューションで提供されます。(ソフトウェア・ディストリビューションに含まれている) コンフィグレーション・ファイルDemo.jneには、同じリンクトポロジーと、このチュートリアルで説明したリンク設定の大部分が含まれています。

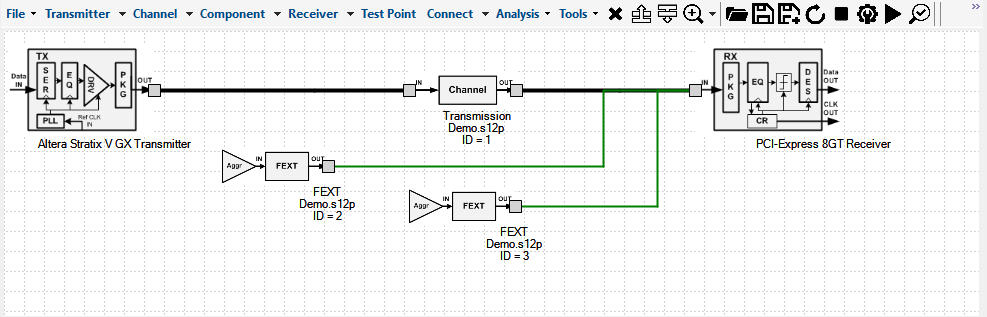

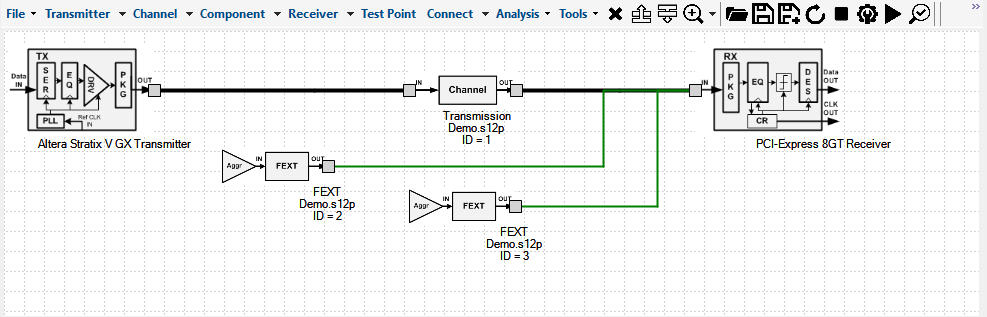

このチュートリアルでは、インテル Stratix® V GXトランスミッターおよび汎用 PCI Express* 8GTレシーバーを備えた典型的な PCI Express* 8GTシステムを近似するリンクが構築され、Advanced Link Analyzerでシミュレートされます。次の図に、リンクトポロジーを示します。

注: このリンク・コンフィグレーションとシミュレーションは、デモンストレーションを目的としており、実際の実装を意図したものではありません。実際の高速リンクのデザインと実装については、インテルのデザイン・ガイドラインを参照してください。

図 188. PCI Express* 8GTのリンクトポロジーの例