インテルのみ表示可能 — GUID: nik1412379636551

Ixiasoft

インテルのみ表示可能 — GUID: nik1412379636551

Ixiasoft

3.1. メソドロジー

このシミュレーションでは、インテル Stratix® V Gxトランスミッター (組み込みパッケージモデルを使用)、 PCI Express* 8GTレシーバー (組み込みパッケージモデルを使用)、および~18インチのバックプレーン・チャネルをエミュレートします。 PCI Express* 8GT仕様に従って、リンクは8 Gbpsで動作し、ビット・エラー・レート (BER) < 10–12です。トランスミッターは、800 mVの最小差動出力電圧と~35 psの立ち上がり/立ち下がり時間 (0.8 V VOD) を備えている必要があります。このシミュレーションでは、 Stratix® V GXトランスミッターは800 mV VOD (VODレベル = 40) に設定されています。さらに、 Stratix® V GXトランスミッターには、チャネル効果を補正するための4タップFIRがあります。 PCI Express* 8Gレシーバーには、PCI-SIG定義ごとにCTLEおよび1タップDFEがあります。

これらの目標を達成するには、トランスミッター・モデル、レシーバーモデル、および次のパラメーターを使用してリンクを設定します。

- データレート: 8 Gbps

- テストパターン: PRBS-23

- BERターゲット: BER < 10–12

- Stratix® V GXトランスミッター

- VOD: 800mV (VOD Level = 40)

- エッジレート: Stratix® V GXの特性による

- 4タップTX FIR (1プリタップおよび2ポストタップ)

- Stratix® V Gxパッケージモデル (組み込み)

- PLL: ATX (LC) を低帯域幅に設定

- Output Jitter: インテル Characterization Databaseから取得 (Advanced Link Analyzerに組み込まれています。この機能をイネーブルするには、マイ・インテル・サポートにお問い合わせください。)

- DCD = ~0.012 UI

- BUJ = ~0.032 UI

- RJ = ~1.00 psRMS (8 Gbps、BER < 10–12)

- レシーバー

- CTLE:

- 4 GHzで6 dB~12 dBのブーストでプログラム可能

- PCI-SIG仕様ごと

- 1タップDFE

- PCI-SIGレシーバー・パッケージ・モデル (PCI-SIGの12ポートSパラメーター・モデル)

- CDR: 高ループ帯域幅~26 MHzの一般的なバイナリーCDR

- Receiver Jitter:

- DJ = ~7 ps

- RJ = ~1.55 psRMS (BER < 10–12)

- CTLE:

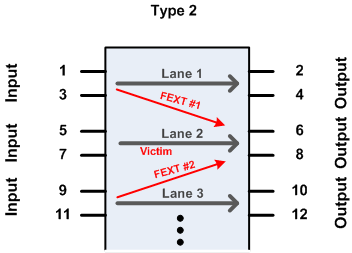

~18インチのバックプレーン・チャネルは、12ポートSパラメーター・モデルによって記述されます。Sパラメーターは、次の図に示すように、ポート・コンフィグレーション・タイプ2で測定 (または生成) されます。

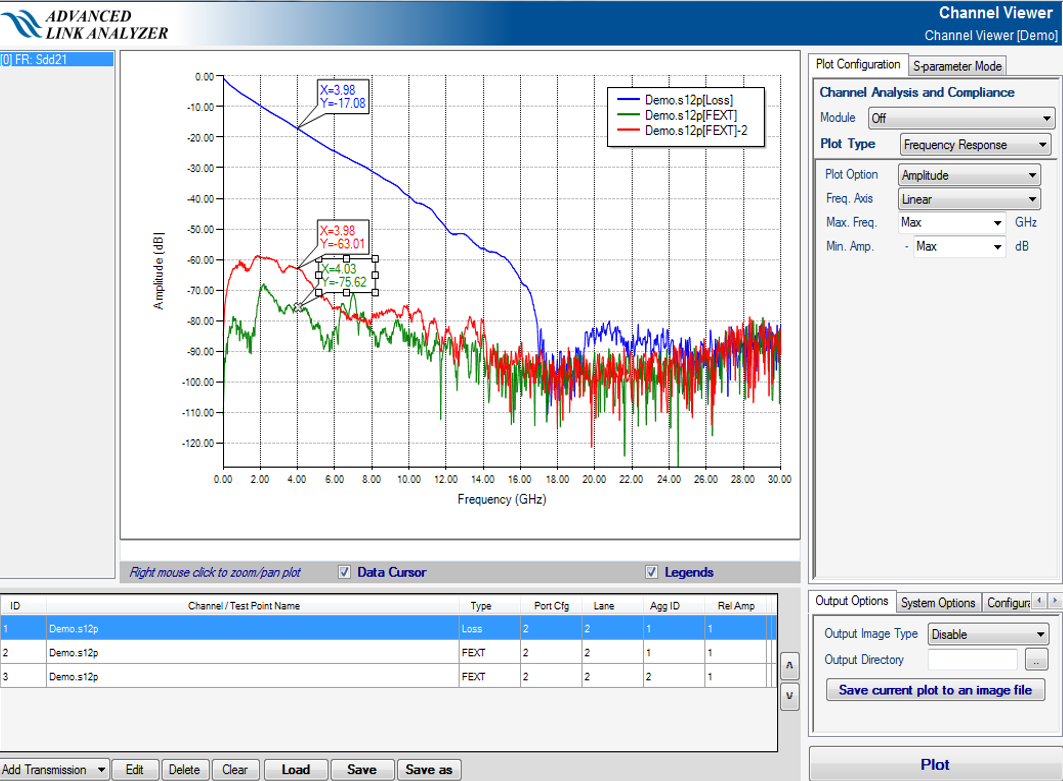

Advanced Link Analyzer Channel Viewerは、バックプレーン・チャネルに4 GHzで約17.15 dBの損失があることを示しています。PCI-SIG RXパッケージには、4 GHzで3.5 dBの挿入損失があります。リンク全体には、4 GHzで約21 dBの損失があります (Combined Channelの黒い曲線に示されているように、 Stratix® V GXトランスミッター・パッケージは含まれません)。必要なBERターゲットを達成するには、TXおよびRXの大幅なイコライゼーションが必要です。

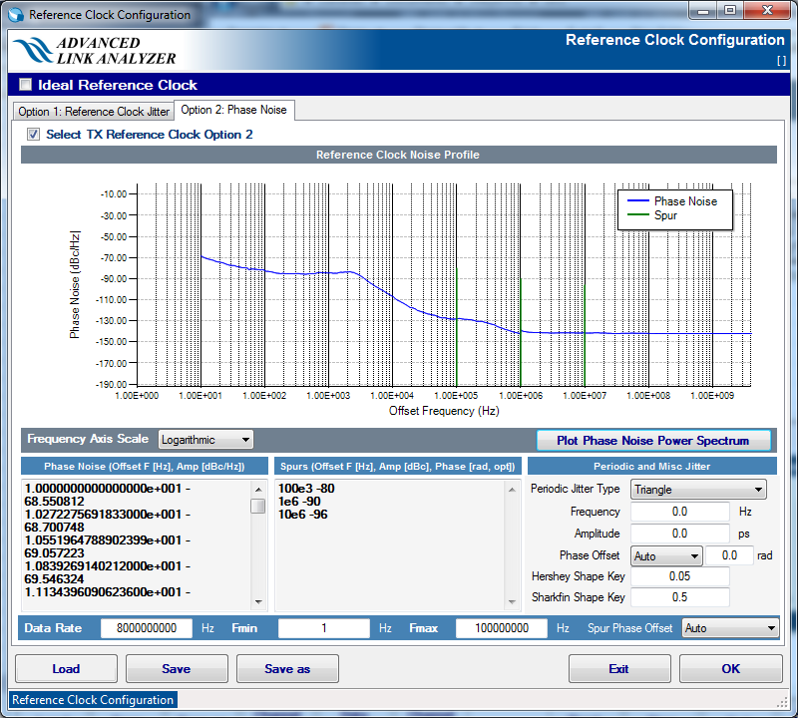

比較する目的で、次の表および図に、典型的な外部100 MHzトランスミッター・リファレンス・クロックおよび、3つの異なる周波数で測定された位相ノイズ特性とスプリアスを示します。

| 位相ノイズ |

スプリアス |

||

|---|---|---|---|

| 周波数 |

位相ノイズ (dBc) |

周波数 |

振幅 (dBc) |

| 10 Hz |

-68 |

100 kHz |

-80 |

| 100 Hz |

-82 |

1 MHz |

-90 |

| 1 kHz |

-84 |

10 MHz |

-96 |

| 1 MHz以上 |

-140 |

||

Stratix® V GXトランスミッターのPLLは、低帯域幅コンフィグレーションのATX (LC) を使用してイネーブル化されます。PLLは、外部リファレンス・クロックからのノイズの影響を効果的に低減します。

Advanced Link Analyzerのリンク最適化アルゴリズムを使用して、トランスミッターとレシーバーの両方に最適なイコライゼーション設定を見つけます。このデモでは、CTLE=>FIR+DFEリンク最適化手法を使用します。