インテルのみ表示可能 — GUID: hqc1620321295716

Ixiasoft

4.7.2.2. グラフィカル・インターフェイスを使用したコンフィグレーション・ファイルの作成

次の例では、GUIモードでProgramming File Generatorを使用して、HPS先行のブートモード用のAVSTコンフィグレーション・ファイルを作成します。

- qpfgw コマンドを実行して、Programming File Generatorモードを起動します。

- Device FamilyにIntel Agilexを選択します。

- Configuration modeにAVST x8、 AVST x16 またはAVST x32を選択します。

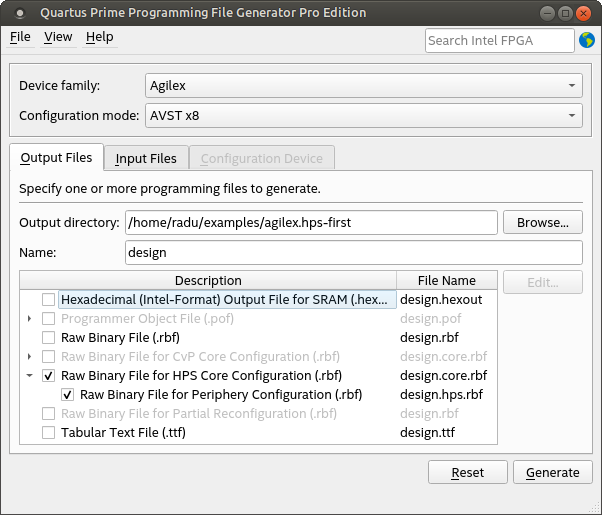

- Output Filesタブで、

- 出力ファイルのNameを「design」に変更します。

- Raw Binary File for HPS Core Configuration (.rbf) オプションをチェックします – その他はグレー表示されます。

- Raw Binary File for Periphery Configuration (.rbf) サブオプションをチェックします。

インテル® Quartus® Prime Programming File Generatorウィンドウの表示は、次のとおりです。図 25. インテル® Quartus® Prime Programming File Generator Pro Editionウィンドウ: Output Files

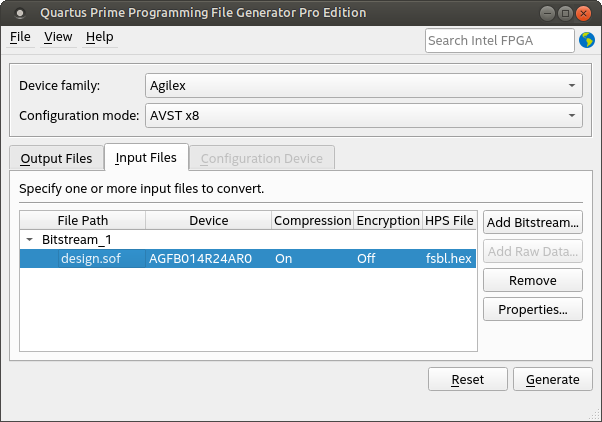

- Input Filesタブにクリックして切り替えます。Input Filesタブで、次の手順を実行します。

- Add Bitstreamボタンをクリックし、SOFファイルを参照して、Openをクリックします。

- 新しく追加した design.sof ファイルをクリックし、Propertiesをクリックします。HPS settings > Bootloaderセクションで、“..”参照ボタンをクリックし、HPS FSBL hexファイルの位置に移動して選択したら、Openをクリックします。

インテル® Quartus® Prime Programming File Generatorウィンドウの表示は、次のとおりです。図 26. インテル® Quartus® Prime Programming File Generator Pro Editionウィンドウ: Input Files

- Generateボタンをクリックします。ファイルが生成されると、確認メッセージが受信されます。

- 必要に応じて、File > SaveまたはFile > Save Asに移動して、コンフィグレーションを .pfg ファイルに保存します。「quartus_pfg -c <filename.pfg>」のようなツールのコマンドライン・バージョンを実行して同じオプションを適用することにより、出力を再度生成できます。