インテルのみ表示可能 — GUID: joc1463592498768

Ixiasoft

インテル® Stratix® 10デバイスおよびトランシーバー・チャネル

PCBスタックアップ選択のガイドライン

高速信号PCB配線に関する推奨事項

FPGAファンアウト領域のデザイン

CFP2/CFP4コネクター・ボード・レイアウトのデザイン・ガイドライン

QSFP+/zSFP/QSFP28コネクター・ボード・レイアウトのデザイン・ガイドライン

SMA 2.4 mmレイアウトのデザイン・ガイドライン

Tyco/Amphenol Interlakenコネクターのデザイン・ガイドライン

電気的仕様

AN 766: インテル® Stratix® 10デバイス 高速信号インターフェイス・レイアウトのデザイン・ガイドライン 文書改訂履歴

インテルのみ表示可能 — GUID: joc1463592498768

Ixiasoft

Interlakenチャネル・インターフェイスのパフォーマンス例

この例にあるチャネルのデザインは、TYCO Interlakenコネクターを使用したInterlakenインターフェイス用です。上記のボードレイアウトに関する推奨事項は、このチャネルデザインで使用します。このデザイン例は、 インテル® Arria® 10デバイス開発キットで実装します。

TXチャネルがこの3D HFSSシミュレーション用に選択されています。TXチャネルのレイヤー26での配線には、レイヤー27までバックドリルを使用します。PCB配線の合計は、角の丸いストリップライン配線を使用した場合、約3.94インチです。

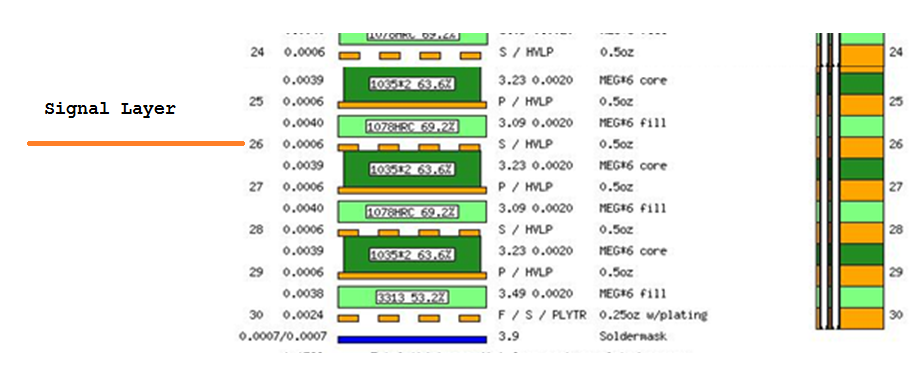

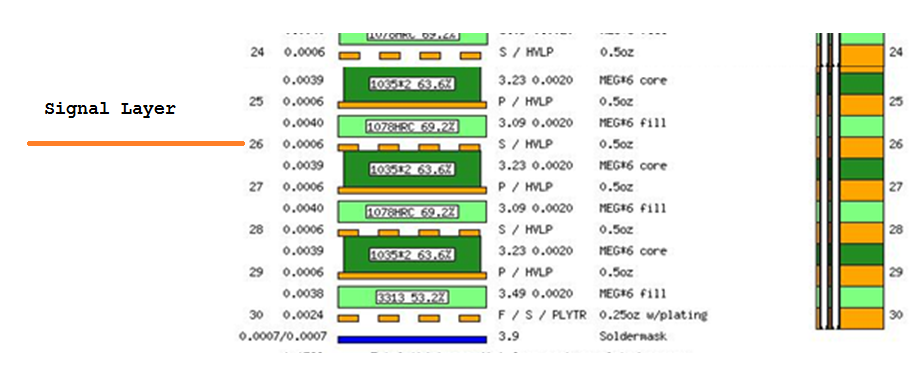

図 105. Interlakenチャネル例のスタックアップ・レイヤーおよび材料データチャネル例の仕様は次のとおりです。

- 30層

- 銅箔-HVLP

- 表面粗さ= 2 µm

- バックドリル

- 材料 = Megtron6

- 総厚 = 153.3 mil

図 106. シミュレーション用Interlaken TXチャネル

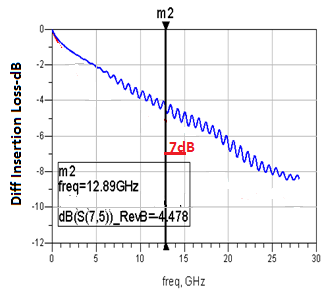

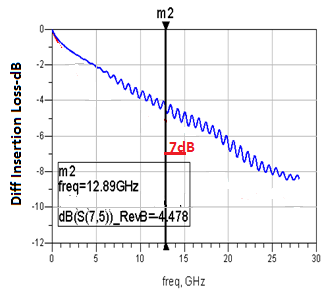

次の図で示すのは、FPGA BGA/ボールから最上位レイヤーのInterlakenコネクター信号パッドまでのホストPCB TXチャネルのパフォーマンスです。

図 107. ホストPCBのみでの差動挿入損失結果にはInterlakenコネクターは含まれません。

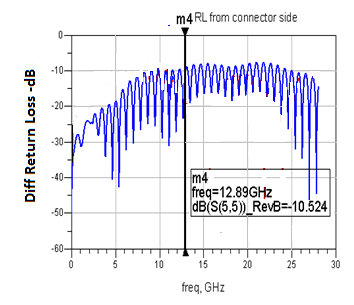

図 108. PCB上のInterlaken コネクターパッドからの差動リターン損失結果にはInterlakenコネクターは含まれません。

挿入損失は、電気的仕様の章に記載されている仕様を下回っています。この仕様で指定しているホストPCBの挿入損失は7 dB未満です。

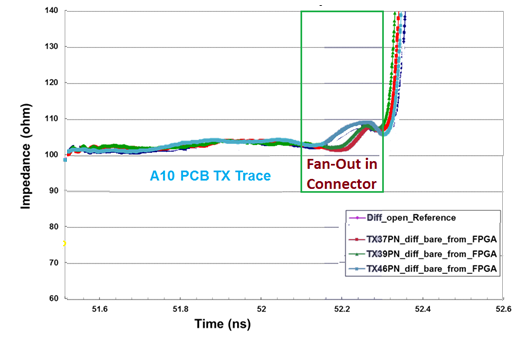

図 109. Arria 10デバイス開発キットのさまざまなTX Interlakenチャネルの差動測定TDRパフォーマンスこの結果で示しているのは、さまざまなTXチャネルのPCBトレース・インピーダンスとコネクター・ファンアウト領域のみに焦点を合わせたパフォーマンスです。

関連情報