インテルのみ表示可能 — GUID: joc1463348716654

Ixiasoft

インテルのみ表示可能 — GUID: joc1463348716654

Ixiasoft

CFP4コネクタ―配線トポロジーのデザイン例

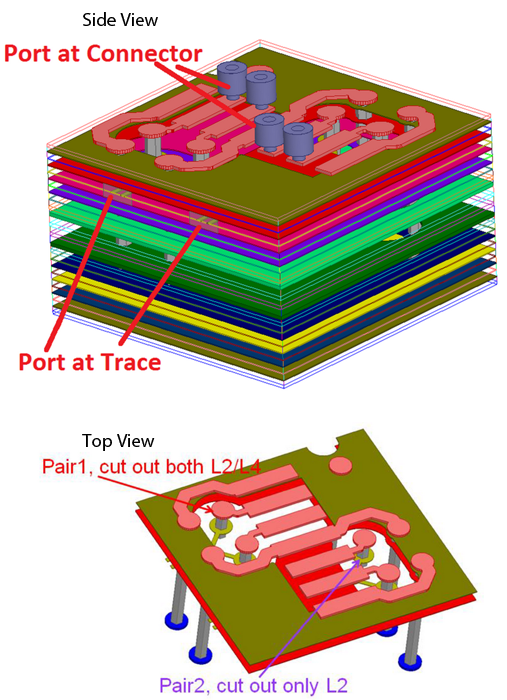

次の図では、CFP4コネクターがシミュレーションに含まれていないことに注意してください。このデザイン例では、117 mil厚の標準24層スタックアップを使用しています。スタックアップ材料はMegron6で、8つの信号レイヤーと4つのPDRレイヤーがあります。

チャネルトレース配線は、上記のペア両方のレイヤー5にあります。Pair1には、コネクターパッド直下にGNDカットアウト (レイヤー2および4) が2つあります。一方Pair2には、レイヤー2にGNDカットアウトが1つだけあります。

Pair2のレイヤー4にGNDカットアウトがない理由は、トレース配線がコネクターパッド直下に配線されて通過する際にリファレンスGNDプレーンが必要なためです。これにより、最小チャネルパスを取得できます。これに対して、反対方向からブレークアウトしてループバックした場合は、より長いチャネルパスが作成されます。

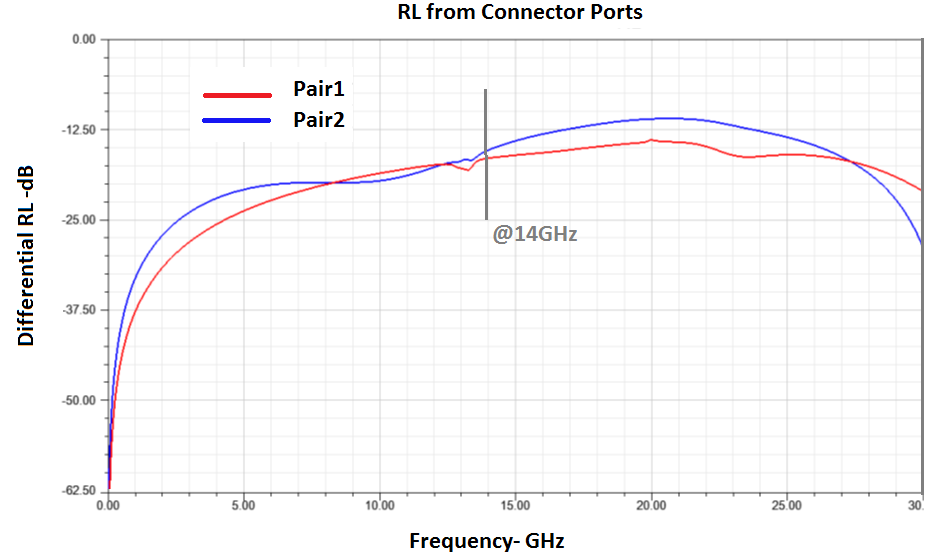

次の図は、Pair1とPair2のパフォーマンスの比較です。

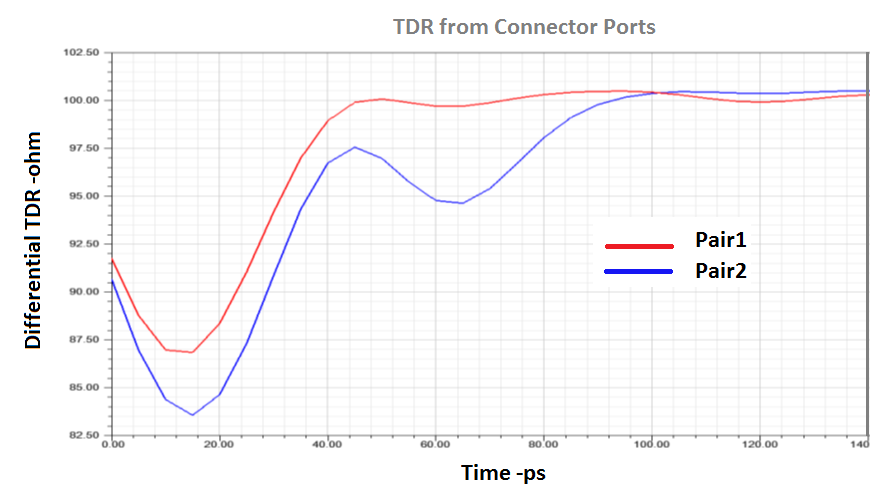

簡単な比較により、Pair2では、15 GHz帯域幅内で最大0.2 dBの挿入損失があることがわかります。これは、コネクターパッド直下の余分な配線長に加えて、コネクターパッド直下のレイヤー4にGNDカットアウトがないためです。Pair2には、15 GHz帯域幅で最大2.5 dBのリターン損失もあります。

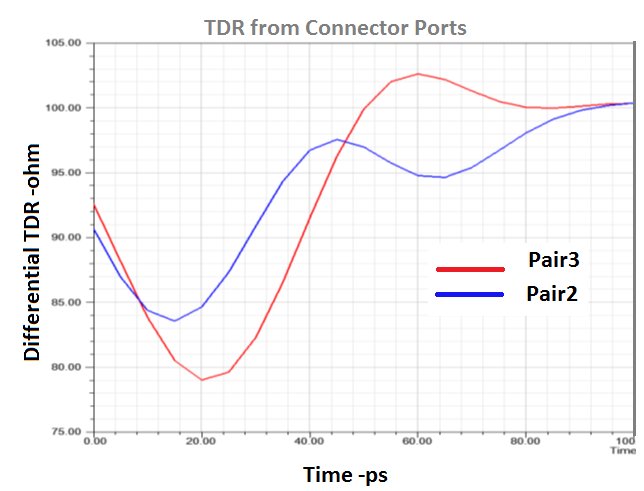

TDR差動インピーダンスは、Pair1のインピーダンス・ミスマッチも小さくなっています。

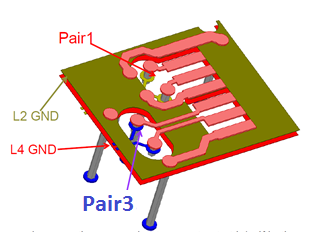

次の図では、レイアウト・コンフィグレーションがPair2 (前の例) からPair3に変更されています。

上の例では、Pair3の信号ビアが左側に移動しています。これにより、GNDカットアウトをCFP4コネクターパッド直下のPair2のレイヤー4に追加できるようになります。このコンフィグレーションでは、Pair3の配線は、信号レイヤー3上にすることができます。Pair1とPair3の両方の合計配線長はこれで等しくなります。

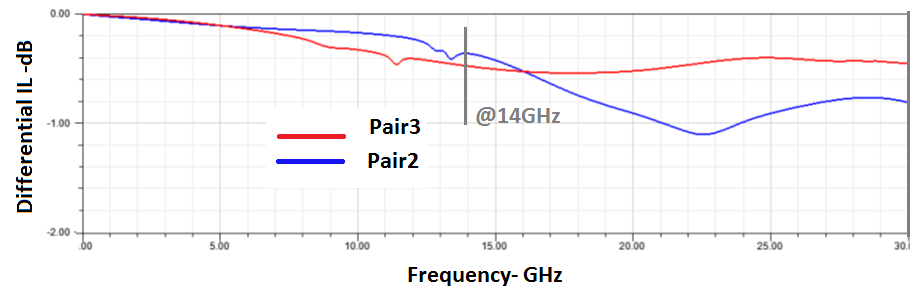

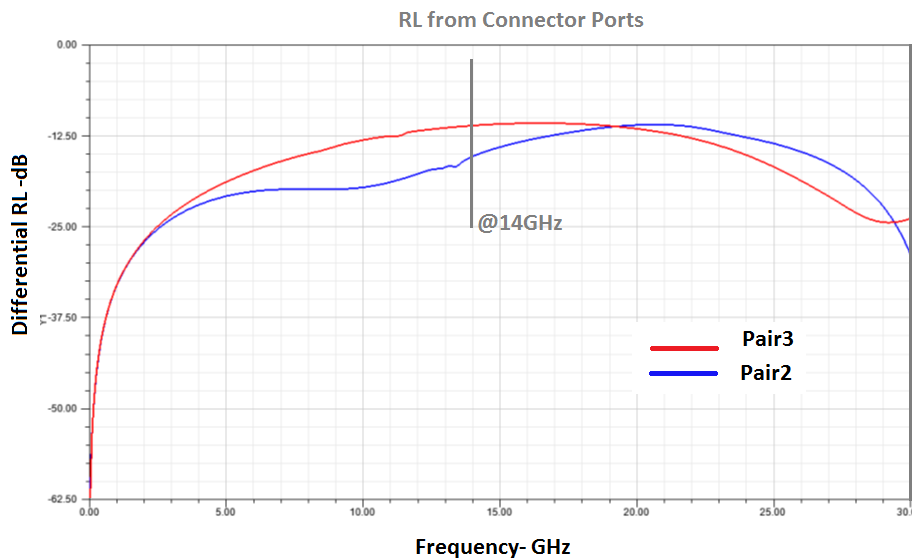

次の図は、Pair2とPair3のパフォーマンスの比較です。

上記の挿入損失およびリターン損失の結果が示しているのは、15 GHz帯域幅内のPair2のパフォーマンスがより優れているということです。これは、CFP4コネクターパッド直下の大きなGNDカットアウト (長方形のカットアウトとアンチパッド経由の信号の組み合わせ) によるものです。これは、TDR差動インピーダンスの結果からも観察されます。ただし、15 GHzより上では、図 60 のPair2は、図 64 のPair3よりもパフォーマンスの低下が大きくなります 。