インテルのみ表示可能 — GUID: tre1628558237707

Ixiasoft

2.2.1.1. 一般的な配線ガイドライン

このセクションでは、高速差動ペアトレースをレイアウトするための配線ガイドラインの概要を示します。

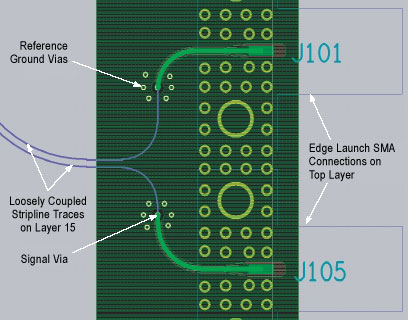

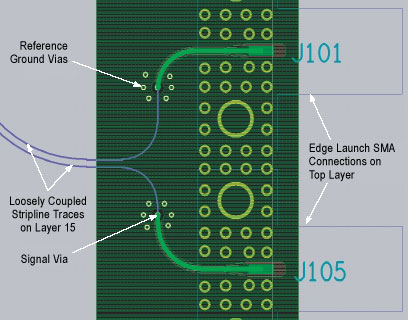

差動トレースには、可能な限り密結合を使用してください。密結合を維持することが、トレースの全長にわたってできない場合は、トレース全体に緩い結合を使用してください。図 7 では、3.125Gbpsの差動トランシーバー・トレースを示しています。これは、 Stratix® GX開発ボードのレイヤー15とその最上位レイヤーで疎結合されています。最上位レイヤーでの密結合は不可能です。これは、必要最小限の分離のため (SMAコネクターの機械的制約のため) です。レイヤー15で密結合を使用した場合、信号は密結合から疎結合に遷移する必要があります。そのため、インピーダンスの不連続性が発生します。

図 7. 疎結合とグランドのリファレンス例

- マイクロストリップとストリップラインの伝送線路は、どちらも配線に適しています。ストリップラインには、他のノイズ源からの信号を遮蔽するという利点もあります。レイアウトデザイン時の制約により、どのレイヤーで配線を行うかが決まることもよくあります。

- 配線の角には丸みを持たせてください。90° の曲がりは、インピーダンスの不連続性をもたらすので、使用しないでください。45° の曲がりは、妥協点です。丸みを帯びた角が最高のパフォーマンスを発揮します。

- ブロードサイド・カップリングとエッジ・カップリングはどちらも問題ありません。一般には、ブロードサイド・カップリングを使用すると、BGAからの配線が容易になりますが、必要なレイヤーの数が多くなります。エッジ・カップリングの場合は、BGAからの配線は困難になりますが、必要なレイヤーの数は少なくなります。どちらでもシグナル・インテグリティーのパフォーマンスは許容可能なものになります。

- 高速信号がプレーン分割をクロスオーバーしないようにしてください。クロスオーバーすると、信号により長いリターンパスが認識され、トレース・インダクタンスが増加します。インダクタンスが増加すると、ラインのインピーダンスが変化し、シグナル・インテグリティーの問題が発生します。

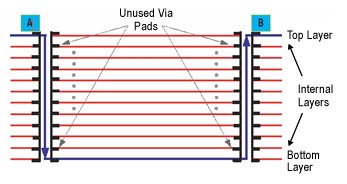

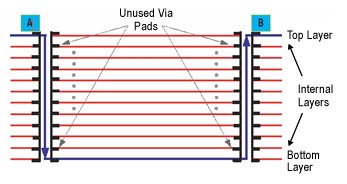

- 未使用のビアパッドは、製造プロセス中にすべて取り外してください。一部の製造会社では、未使用のビアパッドを「機能しないビアパッド」と呼んでいます。未使用のビアパッドにより、信号経路にキャパシタンスが追加されます。図 8 では、未使用のビアパッドの例を示しています。

図 8. 未使用のビアパッド

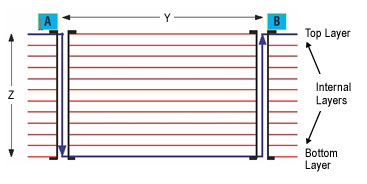

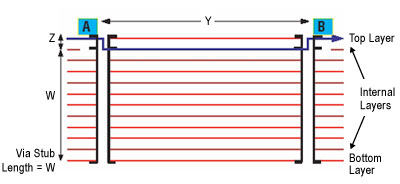

図 9. スルーホール・ビアを使用した最適な配線経路

信号をビア経由で配線する必要がある場合は、ビアスタブの長さが最小になるようにしてください。図 9 で示しているオプションでは、ビアスタブの長さが最小になり、図 10 で示しているオプションよりも優れています。この手法は、 Stratix® GX開発ボードで使われています。高速トレースが最上位レイヤーからレイヤー16までビアを介して取り込まれ、ビアの長さを可能な限り使用し、スタブを最小限が抑えられています。

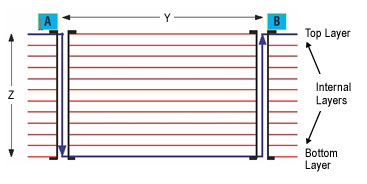

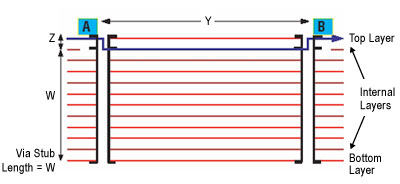

図 10. スルーホール・ビアを使用した準最適配線経路

- デュアル・ストリップライン・トレース (Power 1 – Signal 1 – Signal 2 - Power 2コンフィグレーション) の場合、Signal 1レイヤーの信号が互いに交差する場合は、Signal 2レイヤーの信号と直交させてください。互いに交差しない場合は、少なくとも4W (Wはトレース幅) 離してください。

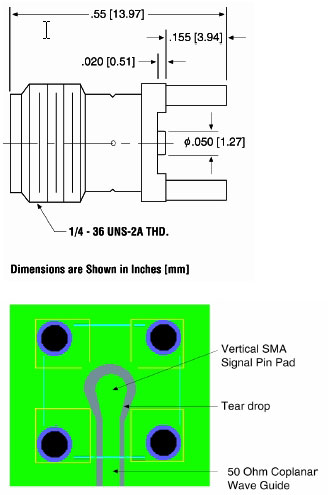

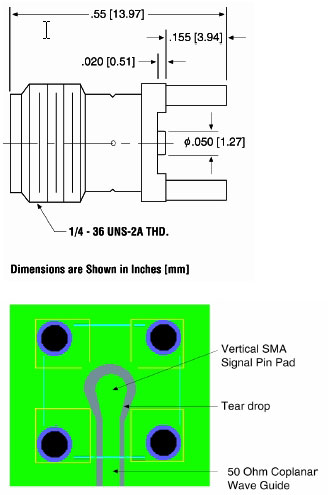

- 「ティアドロップ」を使用して、幅の広いピンとトレースから、幅の狭いピンまたはトレースに移動する場合、インピーダンスの不連続性を減らしてください。例えば、SMAコネクターをトレースに接続する場合は、ティアドロップを使用します。図 11 では、SMAコネクターの寸法と、 Stratix® GX開発ボード上のティアドロップのスクリーンキャプチャを示しています。SMAコネクターのセンターピンは直径50ミルですが、ボードトレースの幅は5ミルになる可能性があります。ティアドロップは、インピーダンスの不連続性を最小限に抑えるのに役立ちます。

図 11. SMAティアドロップ