インテルのみ表示可能 — GUID: puc1508901516211

Ixiasoft

4.2.2. ループの展開

ループが展開されると、各ループのイタレーションは、ハードウェア内で複製され、イタレーションが独立している場合は同時に実行されます。ループを展開すると、FPGA領域使用率が増加し、コンポーネントのレイテンシーが減少します。

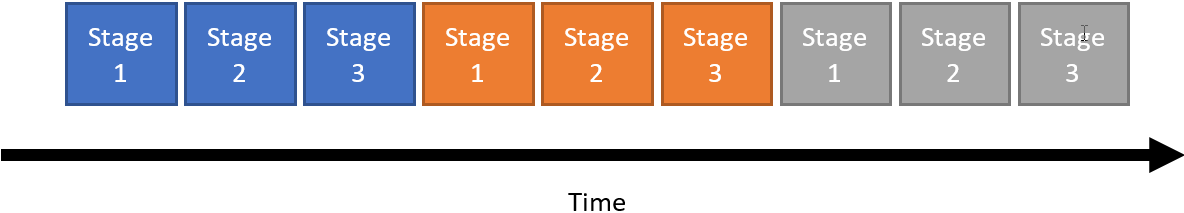

次の基本ループについて検討します。このループには、3ステージと3イタレーションがあります。各ステージで表される動作は、ループで1クロックサイクル内に発生します。

図 8. 基本ループ (3ステージと3イタレーション)

このループの各ステージの実行に1クロックが必要な場合、このループのレイテンシーは9サイクルです。

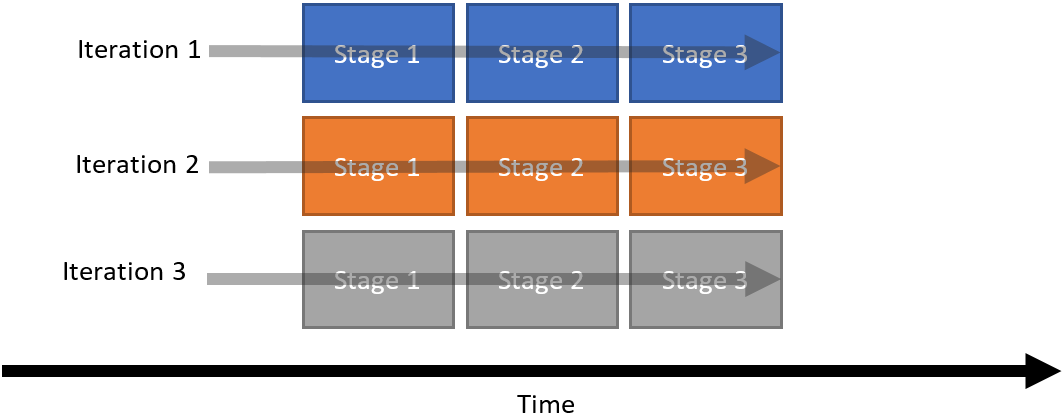

次の図で示しているループは、図 8 のループが3回展開されたものです。

図 9. 展開されたループ (3ステージと3イタレーション)

ループの3イタレーションの完了は、3クロックサイクル内のみで可能ですが、3倍ものハードウェア・リソースが必要です。

コンパイラーによるループの展開方法の制御には、#pragma unroll ディレクティブを使用できますが、このディレクティブが機能するのは、コンパイラーでループのトリップ数を把握している場合、または展開係数を指定した場合のみです。コンパイラーでは、ハードウェアの複製のほかにも、回路の再スケジュールを行います。これにより、各演算は、演算の入力準備ができ次第実行されます。

#pragma unroll ディレクティブの使用例については、best_practices/resource_sharing_filter チュートリアルを参照してください。