インテルのみ表示可能 — GUID: efk1511996063310

Ixiasoft

3.1.1. ポインター・インターフェイス

コンポーネント内のポインターは、 Avalon® Memory Mapped (Avalon-MM) として、デフォルト設定で実装されます。ポインター・パラメーター・インターフェイスについて詳しくは、 Intel High Level Synthesis Compiler Pro Edition Reference Manual内の Intel HLS Compiler Default Interfacesを参照してください。

component void vector_add(int* a,

int* b,

int* c,

int N) {

#pragma unroll 8

for (int i = 0; i < N; ++i) {

c[i] = a[i] + b[i];

}

}

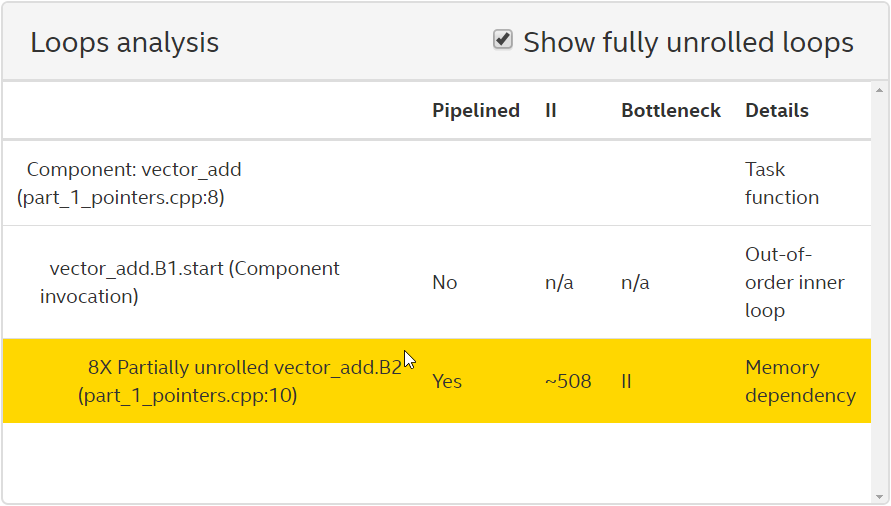

次のLoop Analysisレポートで示しているとおり、コンポーネントのループ開始間隔 (II) が大きくなってしまっています。IIが大きいのは、ベクトル a 、 b 、および c からのアクセスがすべて、同じAvalon-MM Masterインターフェイスを介して行われるためです。 インテル®HLSコンパイラー プロ・エディションでは、ストール可能なアービトレーション・ロジックを使用してこのようなアクセスをスケジュールします。これにより、パフォーマンスが低下し、FPGA領域の使用率が高くなります。

さらに、コンパイラーでは、ループ・イタレーション間にデータ依存関係がないと仮定することはできません。これは、ポインターのエイリアシングが存在する可能性があるためです。コンパイラーでは、ベクトル a 、 b 、および c が重複していないことは、判定できません。データの依存関係が存在する場合、 インテル®HLSコンパイラーでは、ループ・イタレーションの効果的なパイプライン処理はできません。

| QoRメトリック | 値 |

|---|---|

| ALM | 15593.5 |

| DSP | 0 |

| RAM | 30 |

| fmax (MHz)2 | 298.6 |

| レイテンシー (サイクル) | 24071 |

| 開始間隔 (II) (サイクル) | 約508 |

| 1QoRメトリックの計算に使用されたコンパイルフローでは、インテル Quartus Prime プロ・エディションのバージョン17.1を使用しています。 |

| 2fmax の測定値は1シードから計算しています。 |