インテルのみ表示可能 — GUID: ear1527014806057

Ixiasoft

8.2. コンポーネントの結果の品質が悪い

この項内の情報で説明しているのは、ストール可能なアービトレーション・ノードまたは過剰なRAM使用率の一般的なソースについてです。

コンポーネントで予想以上のFPGAリソースを使用する

デフォルトで インテル®HLSコンパイラー プロ・エディションでは、コンポーネントを最適化して最大限のスループットを得るために、最大動作周波数 (fMAX) を最大化しようとします。

領域の消費を削減する方法の1つは、fMAX 要件の緩和です。そのためには、ターゲットfMAX 値の設定を -clock i++コマンドオプションまたは hls_scheduler_target_fmax_mhz コンポーネント属性を使用して行います。HLSコンパイラーでは、多くの場合、指定値よりも高いfMAX を達成します。そのため、ターゲットfMAX rの設定を必要な値よりも低くしても、デザインでは、許容可能なfMAX 値を達成し、消費面積を小さくすることができる場合があります。

fMAX ターゲット値制御の動作について詳しくは、次のチュートリアルを参照してください。 <quartus_installdir>/hls/examples/tutorials/best_practices/set_component_target_fmax

誤ったバンクビット

配列の一部に並列アクセスする場合 (一次元または多次元配列)、メモリーバンクの選択ビットのコンフィグレーションが必要になることがあります。

効率的なメモリーシステムのコンフィグレーション方法について詳しくは、メモリー・アーキテクチャーのベスト・プラクティス を参照してください。

struct 変数の異なる2つの配列にアクセスする条件演算子

場合によっては、struct 変数の異なる配列にアクセスを条件演算子を使用してしようとすると、 インテル®HLSコンパイラー プロ・エディションでは、配列を同じRAMブロックにマージします。Function Memory Viewerには、ストール可能なアービトレーションが表示される場合があります。これは、メモリーシステムに十分なロード/ストアサイトがないためです。

struct MyStruct {

float a;

float b;

}

MyStruct array1[64];

MyStruct array2[64];

MyStruct value = (shouldChooseArray1) ? array1[idx] : array2[idx];

MyStruct value;

if (shouldChooseArray1)

{

value = array1[idx];

} else

{

value = array2[idx];

}

クラスターロジック

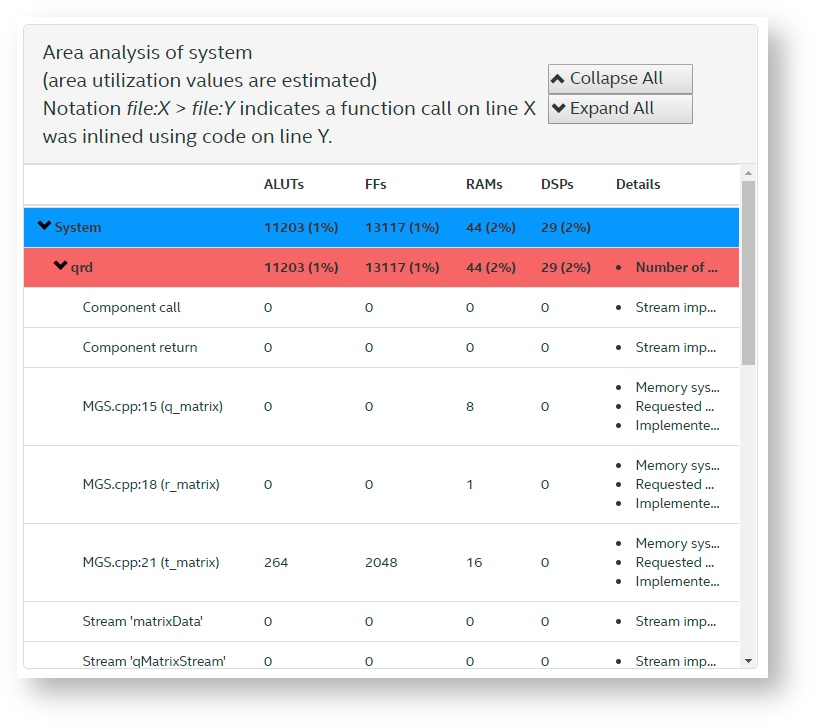

デザインで消費するRAMブロックは、予想より多くなることがあります。これは、多くの配列変数を大きなレジスターに格納する場合は特にそうです。ハイレベルのデザインレポート ( report.html ) のArea Analysis of Systemレポートは、この問題の発見に役立ちます。

3つのマトリックスは、意図的にRAMブロックに格納されます。しかしながら、マトリックスのRAMブロックが占めるRAMブロックは、コンポーネントで消費するRAMブロックの半分未満です。

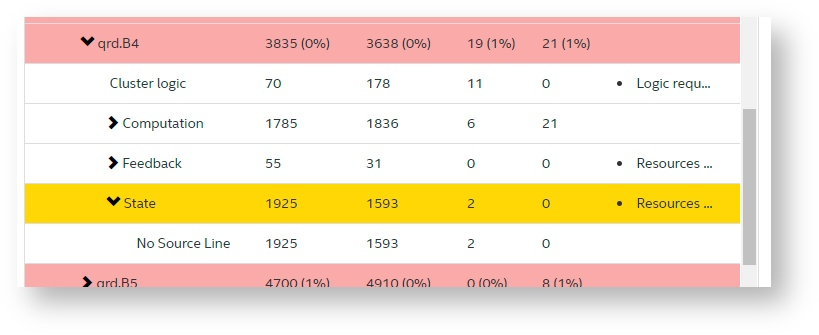

レポートのさらに下を見ると、多くのRAMブロックが、Cluster logicまたはState変数によって消費されていることがわかります。また、レジスターに格納する予定の配列値の一部が、代わりに多数のRAMブロックに格納されていることもわかります。

Cluster LogicおよびStateによって消費されるRAMブロックの数に注意してください。

- ループをパイプライン処理する (ループは展開しない)

- ローカル変数をローカルRAMブロック (hls_memory メモリー属性) に格納 (大きなレジスター (hls_register メモリー属性) には格納しない)