インテルのみ表示可能 — GUID: mzv1511996053473

Ixiasoft

3.1.2. Avalon® Memory Mappedマスター・インターフェイス

デフォルトでは、コンポーネント内のポインターの実装は、 Avalon® -MM (Avalon Memory Mapped) マスター・インターフェイスのデフォルト設定になっています。このデフォルト設定によるパフォーマンスの低下を緩和するには、Avalon-MMマスター・インターフェイスのコンフィグレーションを実行します。

Yベクトル加算コンポーネントの例の Avalon® MMマスター・インターフェイスのコンフィグレーションには、 ihc::mm_master クラスを次のとおり使用します。

component void vector_add(

ihc::mm_master<int, ihc::aspace<1>, ihc::dwidth<8*8*sizeof(int)>,

ihc::align<8*sizeof(int)> >& a,

ihc::mm_master<int, ihc::aspace<2>, ihc::dwidth<8*8*sizeof(int)>,

ihc::align<8*sizeof(int)> >& b,

ihc::mm_master<int, ihc::aspace<3>, ihc::dwidth<8*8*sizeof(int)>,

ihc::align<8*sizeof(int)> >& c,

int N) {

#pragma unroll 8

for (int i = 0; i < N; ++i) {

c[i] = a[i] + b[i];

}

}

メモリー・インターフェイスでは、ベクトル a、ベクトル b、およびベクトル c の場合、次の属性が指定されます。

- ベクトルは、異なるアドレス空間にそれぞれ割り当てられ、 ihc::aspace 属性が指定されます。また、各ベクトルでは、別々の Avalon® MMマスター・インターフェイスを受け取ります。

ベクトルは、異なる物理インターフェイスに割り当てられると、相互干渉することなく同時アクセスが可能になるため、メモリー・アービトレーションは不要です。

- ベクトルでのインターフェイス幅は、ihc::dwidth 属性で調整されます。

- ベクトルでのインターフェイスのアライメントは、ihc::align 属性で調整されます。

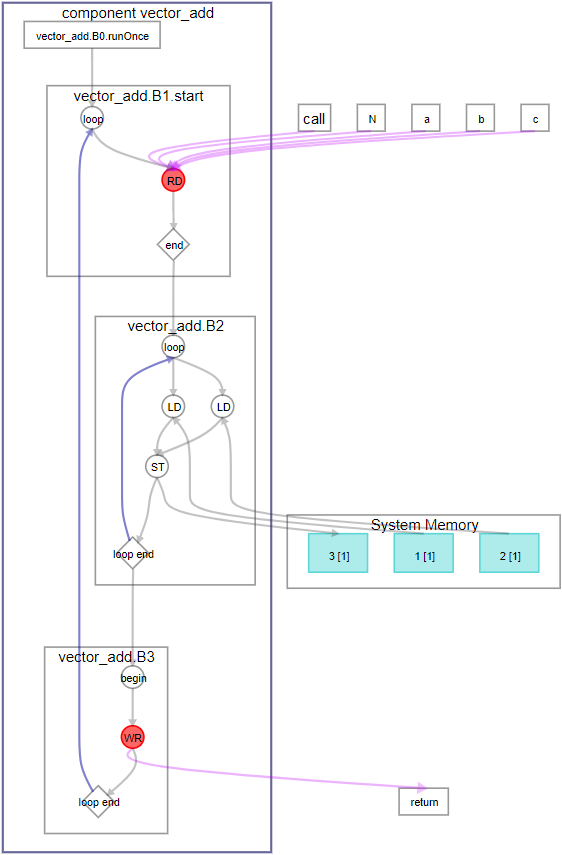

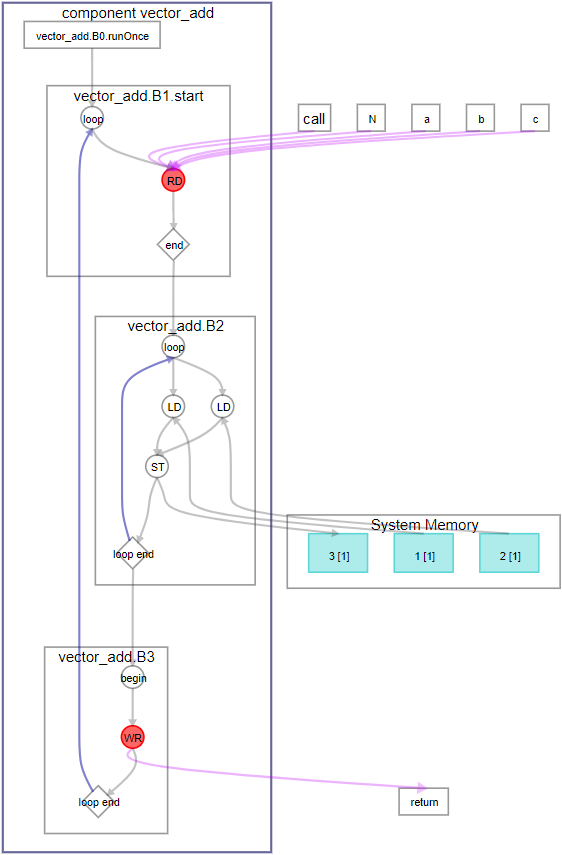

次の図で示すGraph ViewerのFunction Viewは、この例をコンパイルした際に生成されるものです。

図 2. Avalon® MMマスター・インターフェイスでの vector_add コンポーネントのGraph Viewer Function View

この図で示しているとおり、 vector_add.B2 には2ロードと1ストアがあります。 ポインター・インターフェイス のコード例で使用されるデフォルトの Avalon® MMマスター設定には、16ロードと8ストアがあります。

ベクトル・インターフェイスの幅とアライメントを拡張することにより、元のポインター・インターフェイスのロードおよびストアは結合されて、ベクトル a とベクトル b ではそれぞれ 1 ワイドロードに、ベクトルcでは 1 ワイドストア になっています。

また、メモリーはストールフリーです。これは、この例のロードおよびストアから個別のメモリーにアクセスするためです。

このコンポーネントのコンパイルは、 インテル® Quartus® Primeのコンパイルフローを使用して インテル® Arria® 10 デバイスをターゲットとした場合、その結果は次のQoRメトリックになります。

すべてのQoRメトリックは、コンポーネント・インターフェイスを変更して、ポインター・インターフェイスから指定される Avalon® MM Master インターフェイスにすることで改善されます。レイテンシーは、理想レイテンシー値である128に近く、ループの開始間隔 (II) は1です。

| QoR メトリック | ポインター | Avalon MMマスター |

|---|---|---|

| ALM | 15593.5 | 643 |

| DSP | 0 | 0 |

| RAM | 30 | 0 |

| fMAX (MHz)2 | 298.6 | 472.37 |

| レイテンシー (サイクル) | 24071 | 142 |

| 開始間隔 (II) (サイクル) | ~508 | 1 |

| 1QoRメトリックの計算に使用されたコンパイルフローでは、インテル Quartus Prime プロ・エディションのバージョン17.1を使用しています。 |

| 2fmax の測定値は1シードから計算しています。 |

重要: このポインター・インターフェイスから特殊な Avalon® MM Masterインターフェイスへの変更によって、システムでは、メモリーが3つ、それぞれ望ましい幅で必要になります。初回のポインター実装で必要なのは、64ビット幅のデータバスのシステムメモリー1つだけです。必要なメモリーがシステムから提供できない場合は、この最適化は使用できません。