インテルのみ表示可能 — GUID: sth1423703737517

Ixiasoft

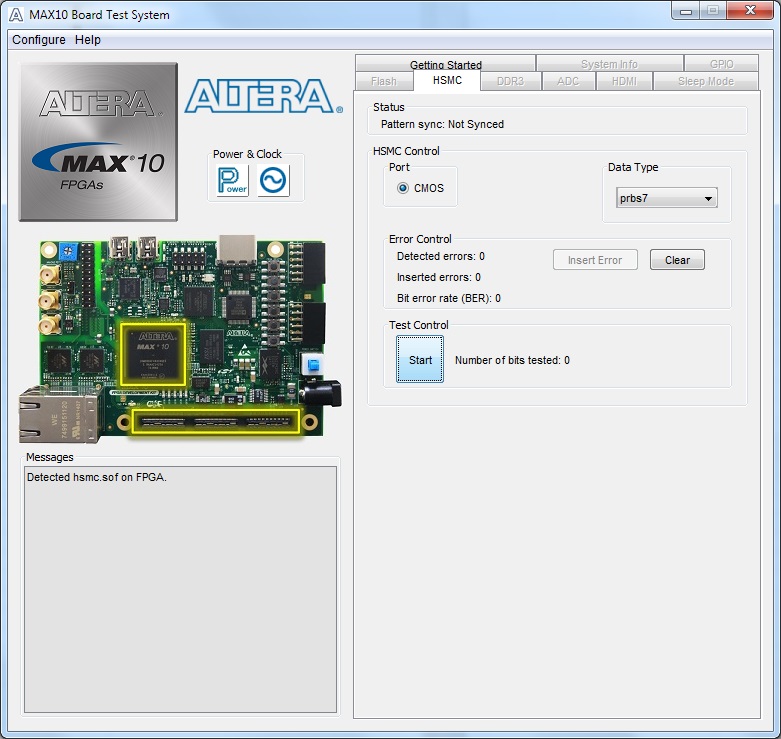

3.5. HSMCタブ

HSMCでは、CMOSポートのテストができます。

図 10. HSMCタブ

| コントロール | 概要 |

|---|---|

| Status | Pattern sync:パターンが同期している状態かどうかを表示します。データ・シーケンスの開始が検出されると、パターンは同期していると考えられます。 |

| Port | CMOS:CMOSポートがテストに使用できます。 |

| Data Type | 以下のデータ型を解析に使用できます:

|

| Error Control |

|

| Test Control |

|