インテルのみ表示可能 — GUID: nik1412640099977

Ixiasoft

3.2.2. 低コストのディスクリート・シーケンサーのシミュレーション結果

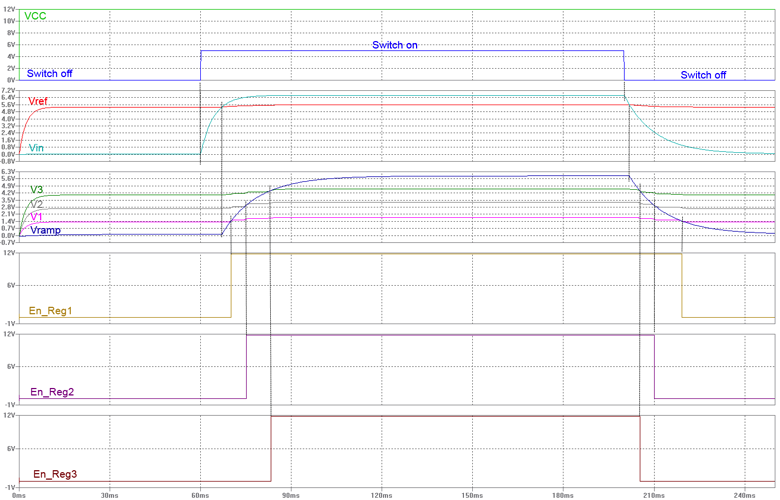

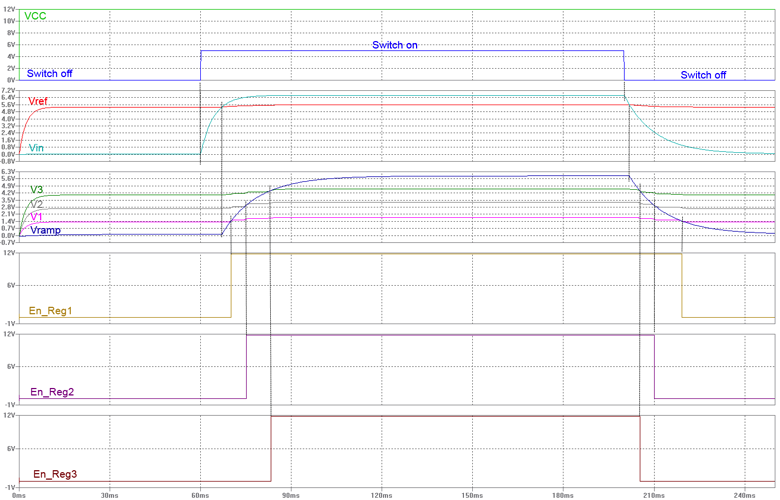

図 10. 電源投入/電源切断イベントの回路シミュレーション結果

パワーオン

最初に、パワースイッチのS1が開いているため、パワー・シーケンサー回路は動作していません。その結果、すべてのレギュレーター・イネーブル (En_Reg1、En_Reg2、およびEn_Reg3) はLowになります。レギュレーター・イネーブルが電圧レギュレーターを駆動するため、すべての電圧レギュレーターはオフになります。- スイッチのS1が閉じている場合、システムがオンになり、電圧VCCがコンデンサーC1を電圧レベルVinまでチャージします。

- C1は抵抗R1を介してチャージされます。電圧レベルVinは、分圧器を形成するR1とR2の値とVin = (R2/(R1+R2))*VCCに依存します。Vinの値がコンパレーターU1Aの基準電圧Vrefよりもやや高くなるように、R1とR2を選択します。

- Vinの値がVrefを上回ると、コンパレーターU1Aの出力がHighとなり、コンデンサーC4が抵抗R5を介してチャージを開始します。

- 抵抗R5とR6はランプ電圧Vrampをセットアップします。抵抗R5とコンデンサーC4は、Vrampのランプレートの時定数を定義します。Vrampは、コンパレーターU1B、U1C、およびU1Dの非反転入力端子への入力電圧です。Vrampが基準電圧 (V1、V2、およびV3) を上回るにつれ、コンパレーターU1D、U1C、およびU1Bを連続してトリップし、レギュレーター・イネーブルEn_Reg1、En_Reg2、およびEn_Reg3をオンにします。

パワーオフ

- 電源切断シーケンスの要件は、電源投入シーケンスの要件と逆順です。

- スイッチS1が開いている場合、システムはシャットダウンを開始します。コンデンサーC1は、R2を介してディスチャージを開始します。R2とC1は、パワーダウン・サイクル中にVinの減衰率を設定します。

- VinがVrefを下回ると、コンパレーターU1Aの出力はオフになります。これは、R5とR6の並列組み合わせを介してVrampをディスチャージします。

- VrampがV3、V2、およびV1より下でディスチャージするにつれ、コンパレーターU1B、U1C、およびU1Dはレギュレーター・イネーブルを順次オフにします。

この回路例は、より多くのレギュレーター・イネーブル (reg_en) 出力をサポートするように簡単に拡張が可能です。

回路を拡張するには、さらに多くのコンパレーターを追加し、抵抗ラダー・ネットワークを拡張して追加の基準電圧比較ポイント (V4、V5など) を生成します。また、Vrampのチャージ/ディスチャージ・レートを上昇させることで、追加のレギュレーター・イネーブル間でより多くの時間を可能とします。この時間遅延は、R5、R6、およびC4によって決定される時定数によって制御されます。