2.5. 合成可能なHigh Bandwidth Memory (HBM2) Interface Intel FPGA IPの高効率生成

合成可能なデザイン例の高効率生成をHBM2インターフェイスで行い、トラフィック効率の測定をIn-System Sources and Probes (ISSP) Editorを使用して行うには、次の手順に従います。

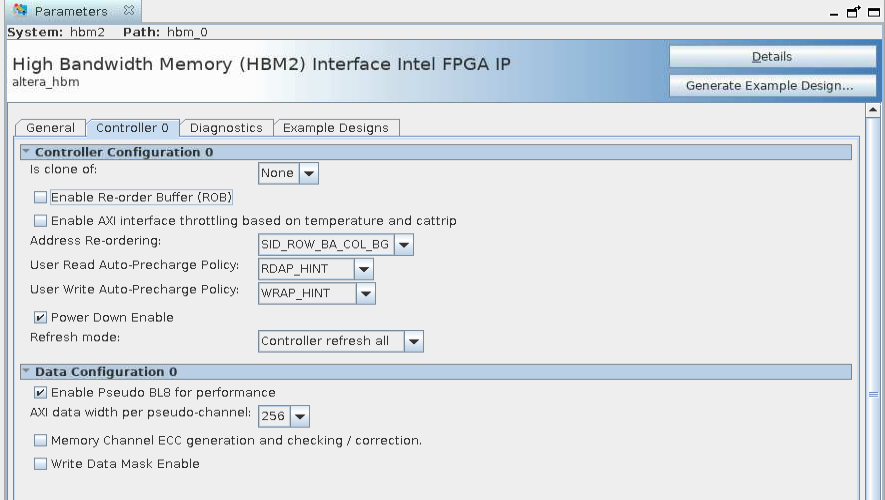

- Controllerタブで、オプションの選択を解除します。Reorder Bufferでは、読み出しデータの並べ替えをリクエストが発行された順序で行います。

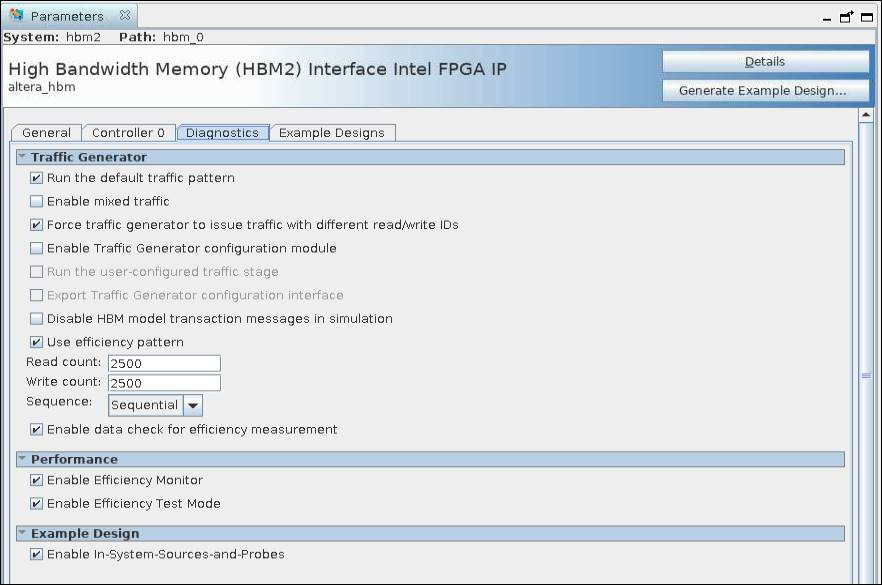

- Diagnosticsタブで、を選択します。またを選択します。

- Read CountとWrite Countの両方の値を最小で 2500に設定して、Sequentialオプションをデータ・トラフィックSequenceとして選択します。(ランダムアドレスを持つトラフィックの効率を測定する場合 、 Sequenceオプションの設定はRandom にします。)

- Diagnosticsタブでを選択します。また、 を選択します。Enable In-System-Sources-and-Probesチェックボックスがまだチェックされていない場合は、Example Designグループボックスでオンにします。

- パラメーター・エディターの右上隅にあるGenerate Example Designをクリックして、合成可能なデザイン例を生成します。

- 開発キットに特定のピン配置を適用し、デザインをコンパイルします。

- デザイン例を回路基板にプログラムしたら、効率性能の結果が取得できます。これには、ISSPエディターを使用します。

- トランザクションの完了の監視と確認が、In-System Sources and Probes (ISSP) EditorのEFFTプローブ上に1で示されます。

EFFR 32ビットプローブ信号で表示するのは、有効な書き込みおよび読み出しトランザクションの値とアクティブなトランザクションの総数です。

EFFWは、3ビット入力セットソース入力信号です。これにより、EFFR 32ビットプローブ信号での出力が可能になります。次の表で示すのは、EFFWの入力値とそれに対応するEFFRカウンターの出力値です。

表 3. EFFWソース値 EFFR出力 (32ビット幅) の説明 3'b 000 有効な書き込みデータ・トランザクションの数です。 3'b 001 有効な読み出しデータ・トランザクションの数です。 3'b 010 アクティブなトランザクションの総数です。 3'b 100 最小読み出しレイテンシーです。 3'b 101 最大読み出しレイテンシーです。

- 効率を計算するには、次の式を使用します。カウンター値に基づいて行います。

Efficiency=[(Number of Write Data transactions + Number of Read Data transactions accepted by HBM2 controller) ÷ (total active transaction count) × [(core clock frequency) × 2) ÷ (HBM2 interface frequency)] × 100.

例えば次の値の場合、

- 書き込みデータ・トランザクション : 5000

- 読み出しデータ・トランザクション : 5000

- アクティブなトランザクションの総数 : 10358

- コアクロック周波数 : 250 MHz

- HBM2インターフェイス周波数 : 600 MHz

効率 = [(5000+5000)÷(10358)×(250)×2÷650]×100=81.3%

- トラフィック・ジェネレーターの実行時に使用する効率パターンは、デフォルトで1つのテストループに対するものです。テストを再開するには、HBM2デザイン例をリセットします。これには、ISSPエディターを使用します。 RSTN信号を使用して、HBM2のデザイン例をリセットするには、0を書き込んでから1を書き込みます。

注: テスト期間と インテル® Stratix® 10 HBM2トラフィック・ジェネレーターのトラフィック・パターンの変更に関する追加情報についての参考ビデオ インテル® Stratix® 10High Bandwidth Memory (HBM2) Traffic Generator は、https://www.youtube.com/watch?v=XLfw12VCm0Uから視聴いただけます。