インテルのみ表示可能 — GUID: ykp1538666715038

Ixiasoft

1. High Bandwidth Memory (HBM2) Interface Intel FPGA IPについて

2. High Bandwidth Memory (HBM2) Interface Intel FPGA IPデザイン例 クイック・スタート・ガイド

3. High Bandwidth Memory (HBM2) Interface Intel FPGA IPデザイン例の説明

4. High Bandwidth Memory (HBM2) Interface インテル® FPGA IPデザイン例 ユーザーガイドのアーカイブ

5. High Bandwidth Memory (HBM2) Interface インテル® FPGA IPデザイン例 ユーザーガイドの改訂履歴

2.1. HBM2システム向け インテル® Quartus® Primeプロジェクトの作成

2.2. High Bandwidth Memory (HBM2) Interface Intel FPGA IPのコンフィグレーション

2.3. High Bandwidth Memory (HBM2) Interface Intel FPGA IP向けIP Parameter Editor Proのガイドライン

2.4. 合成可能なHigh Bandwidth Memory (HBM2) Interface Intel FPGA IPデザイン例の生成

2.5. 合成可能なHigh Bandwidth Memory (HBM2) Interface Intel FPGA IPの高効率生成

2.6. High Bandwidth Memory (HBM2) Interface Intel FPGA IPのシミュレーション用生成

2.7. High Bandwidth Memory (HBM2) Interface Intel FPGA IPデザイン例の変更後の再生成

インテルのみ表示可能 — GUID: ykp1538666715038

Ixiasoft

2.4. 合成可能なHigh Bandwidth Memory (HBM2) Interface Intel FPGA IPデザイン例の生成

インテル® Stratix® 10 MX開発キットでは、High Bandwidth Memory (HBM2) Interface Intel FPGA IPの設定のほとんどは、デフォルト値のままにしておくことができます。 合成可能なデザイン例を生成するには、次の追加手順に従ってください。

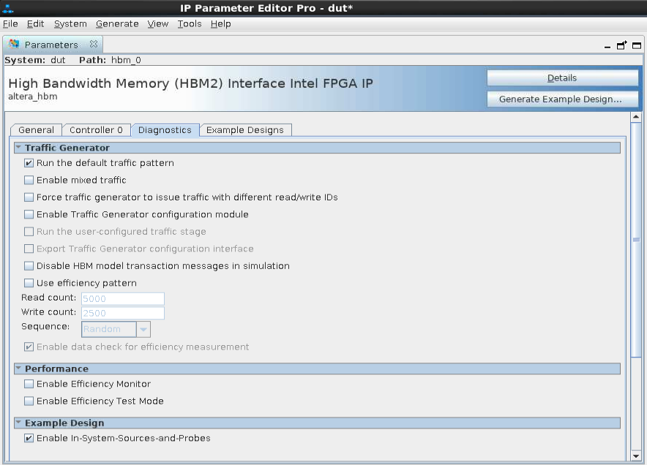

- DiagnosticsタブでExample Design > Enable In-System-Sources-and-Probesを選択すると、デザイン例に統合された使用可能なデバッグ機能へのアクセスが提供されます。

- Diagnosticsタブで、Traffic Generator > Use efficiency patternを選択すると、デザイン例に統合された高効率の同時トラフィック・パターン機能が提供されます。異なる数の読み出し/書き込みトランザクションをコンフィグレーションし、シーケンシャルまたはランダムのトラフィック・アドレス指定を選択し、データ一致チェックをイネーブルまたはディスエーブルします。このオプションでは、 Read command round trip latency機能もイネーブルにします。レイテンシーの測定期間は、有効な読み出しコマンドをドライバーで開始してから、応答が受信されるまでです。

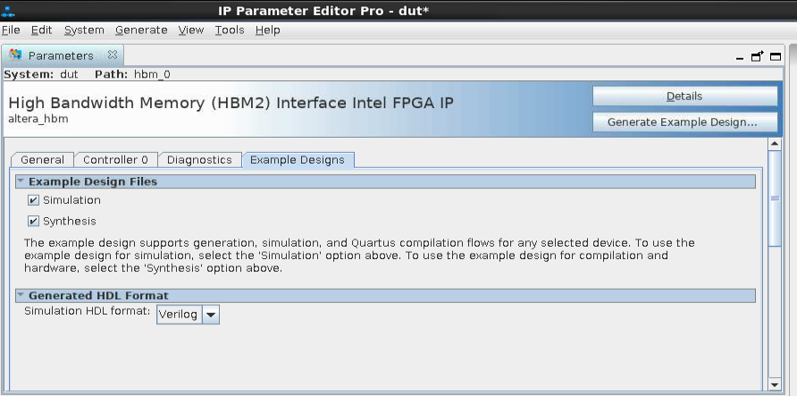

- まだチェックがない場合は、Example DesignsタブのExample Design FilesでSynthesisチェックボックスをオンにします。

注: システムでは、SimulationとSynthesisの両方のチェックボックスをデフォルトでイネーブルします。

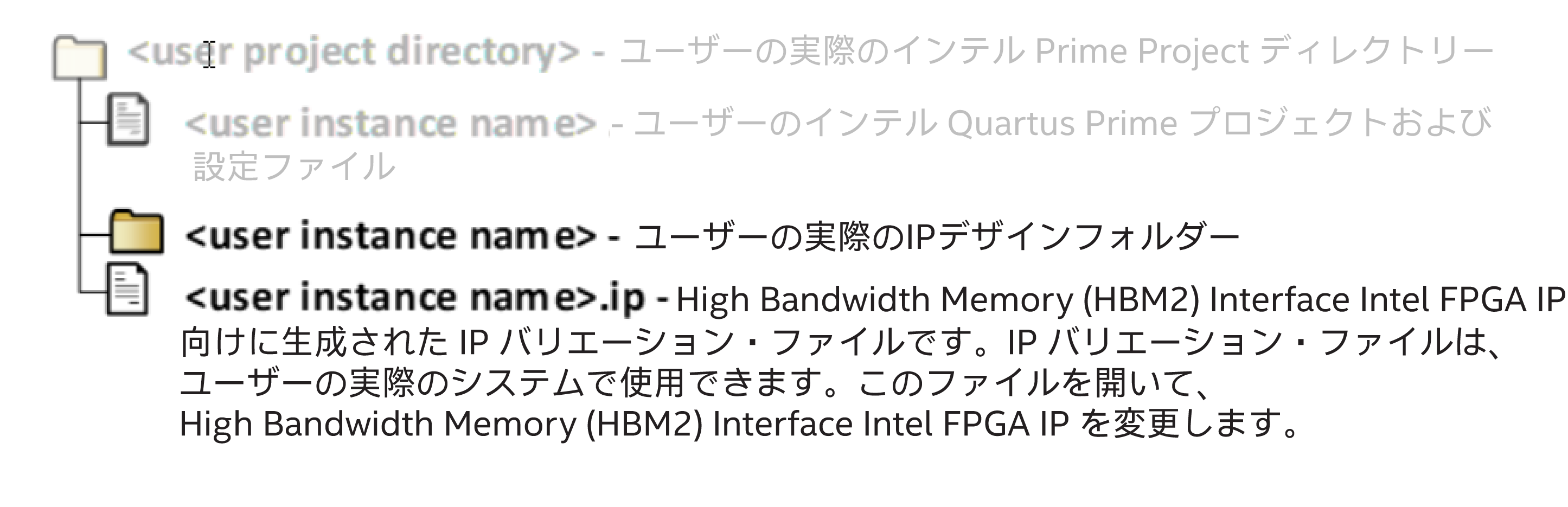

注: システムでは、SimulationとSynthesisの両方のチェックボックスをデフォルトでイネーブルします。 - File > Saveをクリックします。システムでは、現在の設定の作成と保存をユーザーIPバリエーション・ファイル (<user instance name>.ip) で行います。このファイルは、ユーザーが指定した <user project directory> にあります。

- ウィンドウの右上隅にあるGenerate Example Designをクリックします。

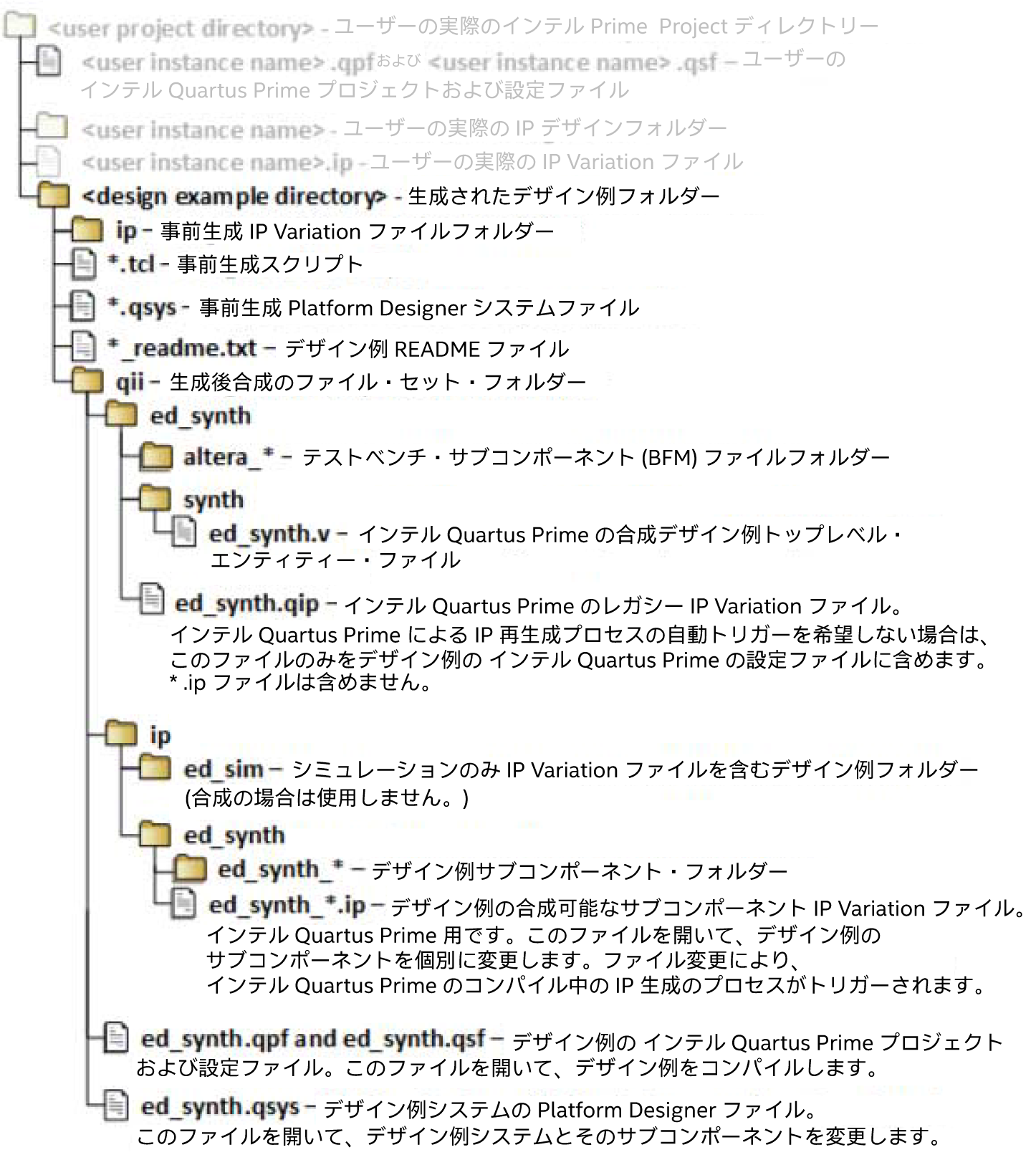

- 生成したデザイン例のディレクトリー (<design example directory>) を指定し、OKをクリックします。システムでは、次のデザイン例ファイルセットを指定されたディレクトリー内に作成します。

- IP Parameter Editor Proウィンドウを終了するには、File > Exitをクリックします。