インテルのみ表示可能 — GUID: nik1412546870121

Ixiasoft

インテルのみ表示可能 — GUID: nik1412546870121

Ixiasoft

5.1.4. CvP 初期化デザインモード向けSOF ファイルの分割

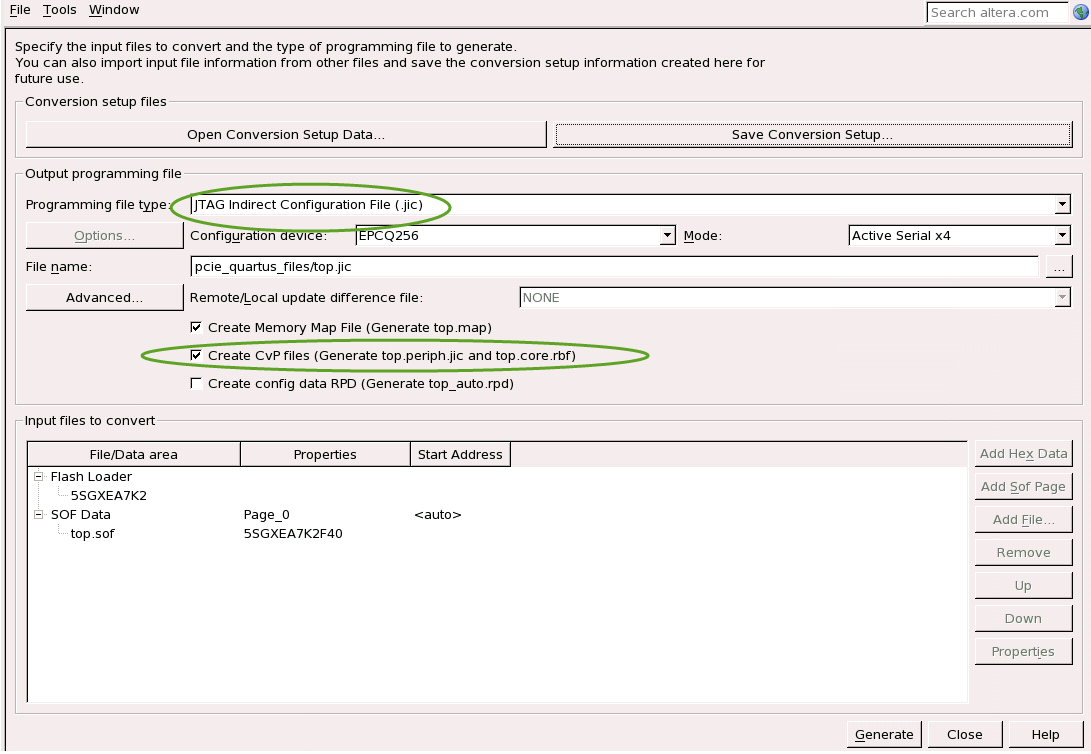

以下の手順に従って、.sof ファイルをペリフェラル・ロジックとコアロジック用に別々のイメージに分割します。

- File メニューでConvert Programming File を選択します。

- Output programming files to convert の下で、以下の表に示すオプションを指定します。

表 11. CvP Initialization Output Programming Files 設定 パラメーター

値

Programming file type

JTAG Indirect Configuration File (.jic)

Configuration device

EPCQ256

Mode

Active Serial x4

File name

./pcie_quartus_files/ ディレクトリーを参照して選択します。ファイル名top.jic を入力します。次にSave をクリックします。

Create Memory Map File

このオプションをオンにします。

Create CvP files

このオプションをオンにします。 このボックスは、Input files to convert の下にSOF Data ファイルを指定するまでグレー表示されます。.

- Input files to convert の下で、以下の表に示すオプションを指定します。

次の図は、指定したオプションを示しています。

表 12. CvP Initialization Input Files to Convert 設定 パラメーター

値

Flash Loader をクリック

Add Device をクリックし、Stratix V と 5SGXEA7K2 を選択し、OK をクリックします。

SOF Data をクリック

Add File をクリックし、./pcie_quartus_files/top.sof に移動します。Device and Pin Options ダイアログボックスで圧縮または暗号化ビットストリームを指定した場合は、Conversion Programming File ウィンドウでも同じオプションを指定する必要があります。これらの設定を有効にするには、top.sof をクリックします。次に、Properties をクリックし、該当するボックスにチェックマークを付けます。 Mode

Active Serial x4

図 20. CvP 初期化モード:プログラミング・ファイルの変換に関する設定

- Output Programming Files セクションのCreate CvP files (Generate top.periph.jic and top.core.rbf) パラメーターをオンにします。

注: このボックスをチェックしないと、Quartus Prime ソフトウェアはペリフェラル・イメージおよびコアイメージ用に別々のファイルを作成しません。

- Save Conversion Setup をクリックして、これらの設定を保存します。この演習では、これらの設定をcvp_base.cof と名付けます。Quartus Prime ソフトウェアは自動的に選択内容を保存しません。

- Generate をクリックして、top.periph.jic とtop.core.rbf を作成します。

注: 生成されたCvP ペリフェラル・ファイルサイズは、選択されたコンフィグレーション・デバイスのサイズと一致します。