インテルのみ表示可能 — GUID: nik1412546857737

Ixiasoft

5.2.1. 高性能リファレンス・デザインのダウンロードと生成

5.2.2. トランシーバー・リコンフィグレーション・コントローラーIP コアの既知の問題の回避策

5.2.3. リコンフィグレーション可能なコア領域の代替user_led.v ファイルの作成

5.2.4. CvP 初期化モード用CvP パラメーターの設定

5.2.5. CvP リビジョンのデザインフローを使用したコアロジック領域のCvP リビジョンの作成

5.2.6. CvP リビジョンのデザインフローにおけるBase とcvp_app の両方のリビジョンのコンパイル

5.2.7. CvP リビジョンのデザインフローによるCvP 初期化モードのSOF ファイルの分割

5.3.1. 高性能リファレンス・デザインのダウンロードと生成

5.3.2. トランシーバー・リコンフィグレーション・コントローラーIP コアの既知の問題の回避策

5.3.3. リコンフィグレーション可能なコア領域の代替user_led.v ファイルの作成

5.3.4. CvP 更新モード用CvP パラメーターの設定

5.3.5. CvP リビジョンのデザインフローを使用したコアロジック領域のCvP リビジョンの作成

5.3.6. CvP 更新モードのデザインのコンパイル

5.3.7. CvP 更新デザインモード向けSOF ファイルの分割

5.3.8. CvP リビジョンのデザインフローによるCvP 更新モードのSOF ファイルの分割

6.3.1. アルテラ定義のVendor Specific Capability Header レジスター

6.3.2. アルテラ定義のVendor Specific Header レジスター

6.3.3. Altera Marker レジスター

6.3.4. CvP Status レジスター

6.3.5. CvP Mode Control レジスター

6.3.6. CvP Data レジスター

6.3.7. CvP Programming Control レジスター

6.3.8. Uncorrectable Internal Error Status Register

6.3.9. Uncorrectable Internal Error Mask Register

6.3.10. Correctable Internal Error Status Register

6.3.11. Correctable Internal Error Mask Register

インテルのみ表示可能 — GUID: nik1412546857737

Ixiasoft

5.1.1. 高性能リファレンス・デザインのダウンロードと生成5.2.1. 高性能リファレンス・デザインのダウンロードと生成5.3.1. 高性能リファレンス・デザインのダウンロードと生成

CvP を有効にしたPCI Express High Performance Reference Design を再生成するには、次の手順に従います。

- PCI Express プロトコルWebページからPCIe AVST and On-Chip Memory Interface デザインファイルをダウンロードしてください。このデザインには、Stratix V GX FPGA 開発キットをターゲットとするための正しいピン・アサインメントとプロジェクト設定が含まれています。

- PCIe_SVGX_AVST_On_Chip_Mem_140.zip を展開します。

- hip_s5gx_x1_g1_ast64_140.qar を作業ディレクトリーにコピーします。

- Quartus Prime ソフトウェアを起動し、hip_s5gx_x1_g1_ast64_140.qar を復元します。

- Tools メニューでQsys をクリックします。

- Top.qsys を開きます。

- System Contents タブでDUT を右クリックし、Edit を選択します。

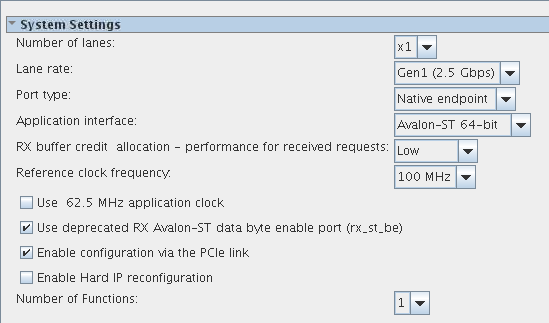

- System Settings の下で、次の図に示すように、Enable configuration via the PCIe link をオンにします。

図 22. 図 36. PCI Express パラメーター・エディター用のハードIP

- Finish をクリックします。

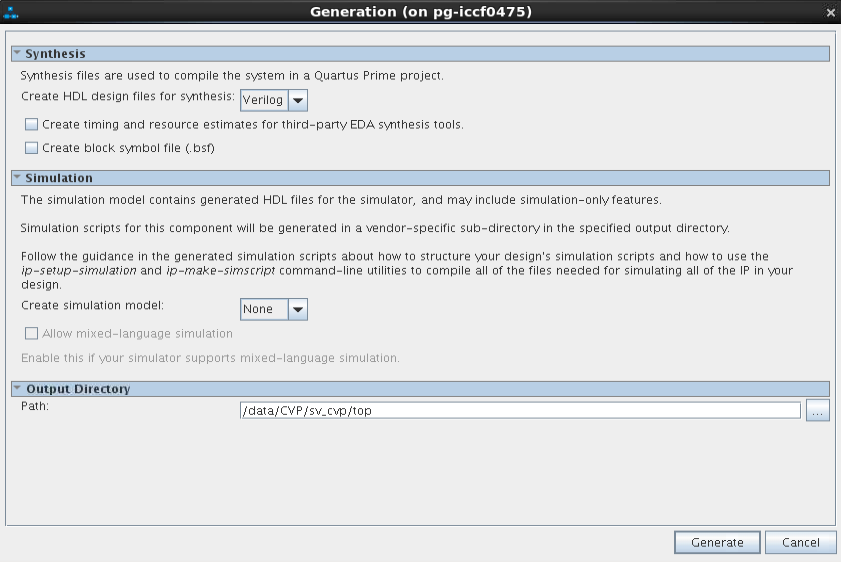

- Generation タブで、次の表の設定を指定します。次に、ウィンドウの下部にあるGenerate をクリックします。

表 13. 表 18. Qsys Generation タブの設定 パラメーター 値 Create simulation model

None

Create testbench Qsys system

None

Create testbench simulation model

None

Create HDL design files for synthesis

Verilog Create block symbol file (.bsf)

この項目をオフにします。

Path

< working_dir> top

Simulation

この項目は空白のままにします。

Testbench

<working_dir> /top /synthesis

図 23. 図 37. Qsys 生成ウィンドウ

- コンパイルが成功したら、Qsys を閉じます。

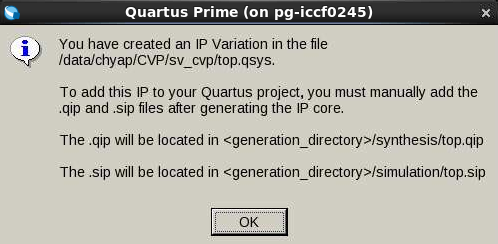

- IP バリエーションを作成した後、このIP をQuartus プロジェクトに追加するには、.qip ファイルと.sip ファイルをマニュアルで追加する必要があります。

.qip は<working_dir>/synthesis/top.qip にあります。.sip は<working_dir>/simulation/top.sip にあります。図 24. 図 38. Quartus® Prime Reminder

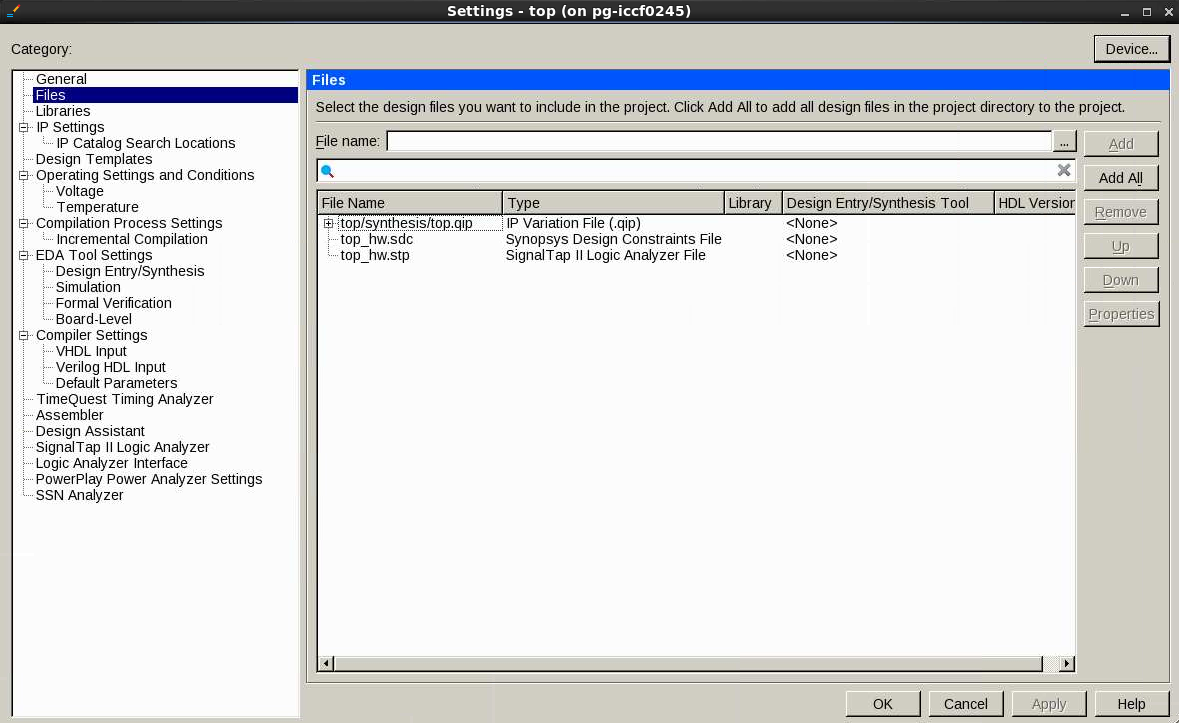

- Assignments メニューでSettings を選択します。

- Files カテゴリーで、既存のtop.qip IP Variation File を削除します。

- <working_dir>/synthesis/top.qip にあるIP コアの生成後に作成された新しいtop.qip ファイルを参照します。

- Add とOK をクリックしてSettings ウィンドウを閉じます。

図 25. 図 39. Settings ウィンド