インテルのみ表示可能 — GUID: etw1623339842180

Ixiasoft

ステップ3: PRパーティションに対する配置と配線領域の割り当て

作成するベースリビジョンごとに、PRデザインフローは対応するペルソナコアをPRパーティション領域に配置します。ベースリビジョンのデバイス・フロアプランでPR領域を見つけて割り当てるには、次の手順に従います。

- Project Navigatorで u_blinking_led インスタンスを右クリックし、 Logic Lock Region > Create New Logic Lock Regionをクリックします。領域は、Logic Lock Regions Windowに表示されます。

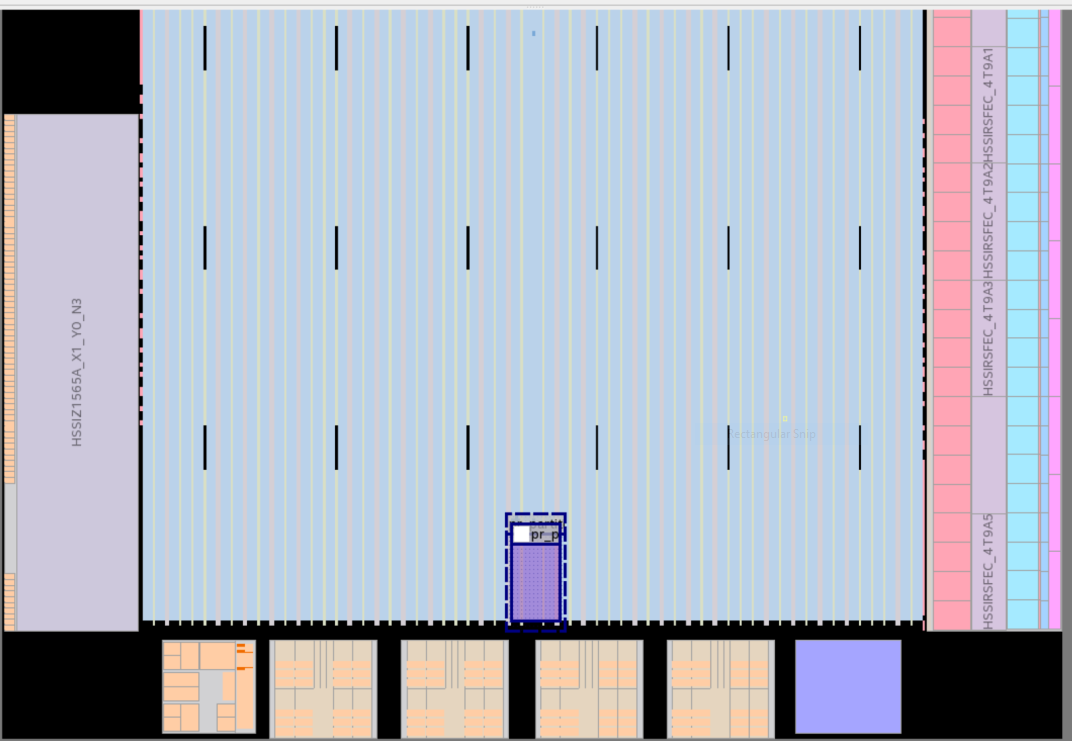

- 配置領域は、blinking_led ロジックを囲む必要があります。Chip Plannerでノードを見つけて、配置領域を選択します。Logic Lock Regions Windowで u_blinking_led 領域名を右クリックし、Locate Node > Locate in Chip Plannerをクリックします。

u_blinking_led 領域は色分けされています。

図 4. blinking_led のChip Plannerノードの位置

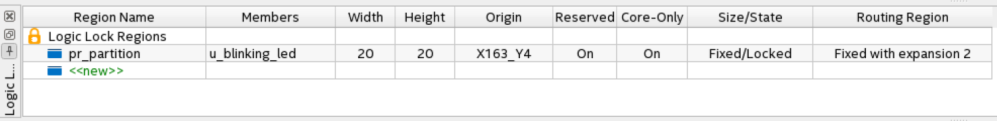

- Logic Lock Regionsウィンドウで、Origin列に配置領域の座標を指定します。原点は、領域の左下隅に対応します。例えば、(X1 Y1) 座標を (163 4) として配置領域を設定するには、Originを X163_Y4 として指定します。インテルQuartus Prime開発ソフトウェアは、指定した高さと幅に基づいて、配置領域の (X2 Y2) 座標 (右上) を自動的に計算します。

注: このチュートリアルでは、(X1 Y1) 座標 - (163 4)、および配置領域の高さと幅を20として使用します。配置領域の値を定義します。領域が blinking_led ロジックをカバーしていることを確認してください。

- ReservedおよびCore-Onlyのオプションをイネーブルします。

- Routing Regionオプションをダブルクリックします。 Logic Lock Routing Region Settingsダイアログボックスが表示されます。

- Routing typeにFixed with expansionを選択します。このオプションを選択すると、拡張長2が自動的に割り当てられます。

注: 配線領域は配置領域よりも大きくする必要があります。これは、エンジンが異なるペルソナを配線する際に、Fitterにさらなる柔軟性を提供するためです。図 5. Logic Lock Regionsウィンドウ

set_instance_assignment -name PLACE_REGION "X163 Y4 X182 Y23" -to \

u_blinking_led

set_instance_assignment -name RESERVE_PLACE_REGION ON -to \

u_blinking_led

set_instance_assignment -name CORE_ONLY_PLACE_REGION ON -to \

u_blinking_led

set_instance_assignment -name ROUTE_REGION "X161 Y2 X184 Y25" -to \

u_blinking_led