インテルのみ表示可能 — GUID: nim1593117209831

Ixiasoft

1.2.3. Platform Designerでの初期HDLの生成

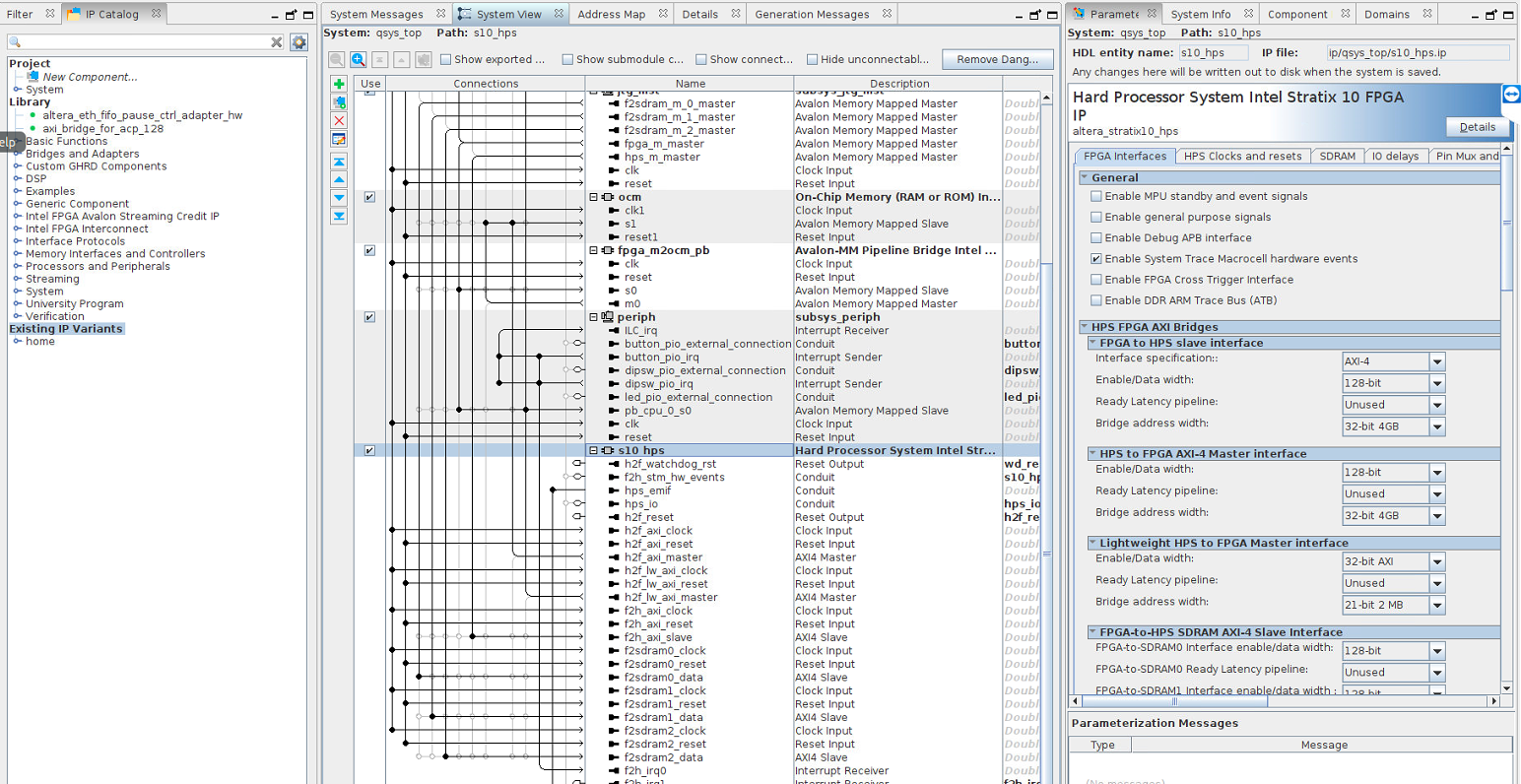

- Quartus Prime Pro Editionナビゲーション・バーで、Tools > Platform Designerを選択します。

- Platform Designerウィンドウで、File > Open > qsys_top.qsys を選択します。

- System Viewタブで、s10_hpsをダブルクリックして、HPS Parametersウィンドウを開きます。

図 2. System Contentsウィンドウ

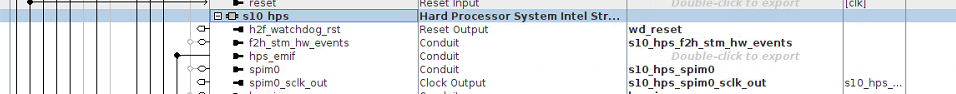

- Pin Mux and Peripherals > Advanced > Advanced FPGA placementに移動し、SPIM0のRoute to FPGAボックスでYesを選択し、Apply Selectionsをクリックします。

- Export列をダブルクリックして、s10_hps.spim0 コンジットをエクスポートします。

- Export列をダブルクリックして、s10_hps.spim0_sclk_out コンジットをエクスポートします。

図 3. エクスポートされた信号

- 新しいGPIOソフトIPを追加して、SPIチップセレクトとして使用します。

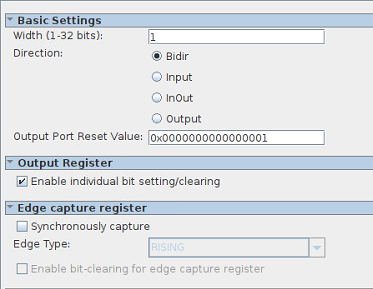

- 新しいコンポーネントのタイプPIO (Parallel I/O) Intel FPGA IPを追加して、spi_cs_pioという名前を付けて、次のようにコンフィグレーションします。

- Width: 1

- Direction: bidir

- Enable individual bit setting/clearing: yes

- Output Port Reset Value: 0x0000000000000001

図 4. PIO設定

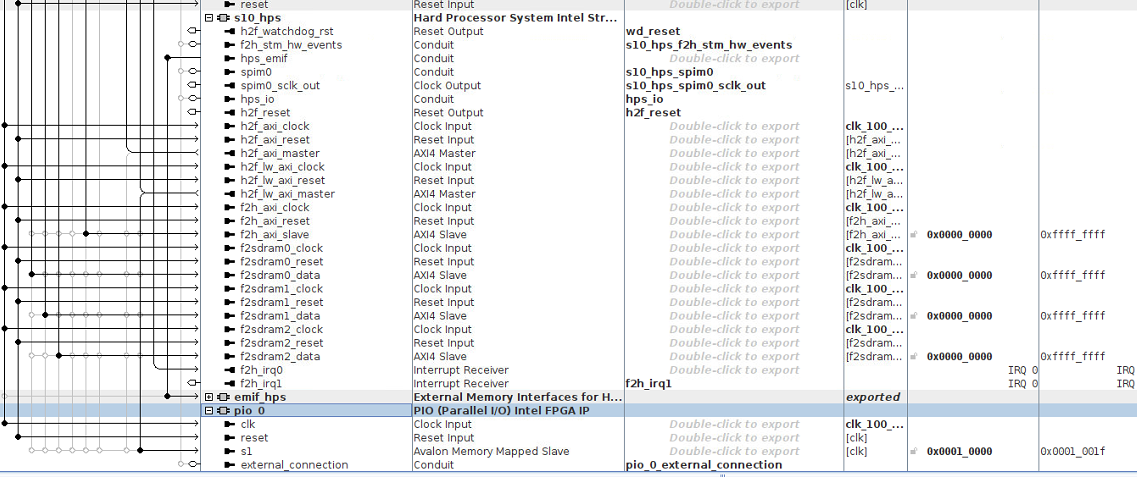

- spi_cs_pio.s1 のベースアドレスを0x0001_0000に変更して、他のIPとの競合を避けます。

- spi_cs_pio を次のように接続します。

clk:: clk_100.out_clk へ接続

reset:: rst_in.out_reset へ接続

s1: s10_hps.h2f_lw_axi_master へ接続

spi_cs_pio.external 接続をダブルクリックしてエクスポートし、コンジットspi_cs_pio.spi_cs_pio_external_connection_exportを作成します。

図 5. PIOの接続

- Generate > Show Instantiation Templateに移動して、テンプレートをファイルに保存し、qsys_topの新しい信号名を取得します。

- Generateボタンをクリックして、システムを生成します。