インテルのみ表示可能 — GUID: eis1414475131951

Ixiasoft

インテルのみ表示可能 — GUID: eis1414475131951

Ixiasoft

4.3.10. 異なる入力幅と出力幅

DCFIFO_MIXED_WIDTHSの機能は、幅の比率が有効な場合に、書き込み入力データと読み出し出力データで異なる幅をサポートします。入力データ幅と出力データ幅の組み合わせが無効な比率になる場合、FIFOのパラメーター・エディターはエラーメッセージを表示します。サポートされている幅の比率は2の累乗で、RAMによって異なります。

IPコアは、幅の広い書き込みポートと幅の狭い読み出しポート (またはその逆) をサポートします。 インテル® Agilex™ デバイスで現在サポートされている混合幅の比率を次の表に示します。

| デバイスファミリー | 有効な幅の比率 |

|---|---|

| インテル® Agilex™ | 1、2、4、8、16、32 |

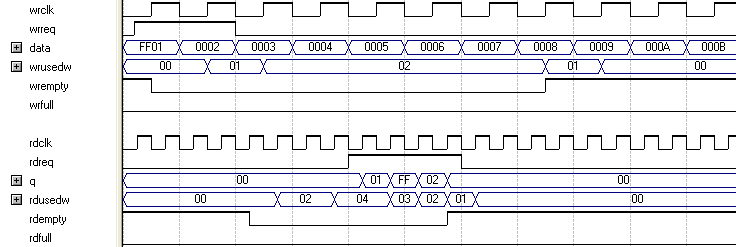

この例では、読み出しポートは書き込みポートの2倍の周波数で動作しています。FIFOバッファーに2つの16ビット・ワードを書き込むと、wrusedwフラグが2に増加し、rdusedwフラグが4に増加します。4つの8ビットの読み出し動作でFIFOバッファーは空になります。読み出しは、書き込まれた16ビット・ワードの最下位8ビットで始まり、最上位8ビットが続きます。

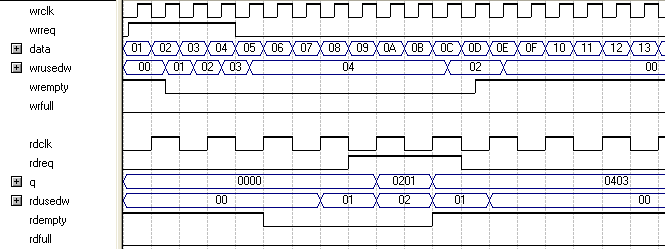

この例では、読み出しポートは書き込みポートの半分の周波数で動作しています。FIFOバッファーに4つの8ビット・ワードを書き込むと、wrusedwフラグが4に増加し、rdusedwフラグが2に増加します。2つの16ビットの読み出し動作でFIFOは空になります。書き込まれた最初と2番目の8ビット・ワードはそれぞれ、16ビットの出力ワードのLSBとMSBに相当します。rdempty信号は、幅の広い読み出しポートのワード全体を満たすのに十分なワードが幅の狭い書き込みポートに書き込まれるまでアサートされたままになります。