インテルのみ表示可能 — GUID: ame1670545308787

Ixiasoft

1. インテル® FPGA Power and Thermal Calculator の概要

2. インテル® FPGA Power and Thermal Calculator での消費電力の見積もり

3. インテル® FPGA Power and Thermal Calculator のグラフィカル・ユーザー・インターフェイス

4. インテル® FPGA Power and Thermal Calculator のページ

5. インテル® FPGA PTC の精度に影響する要素

6. インテル® FPGA Power and Thermal Calculator ユーザーガイドのアーカイブ

7. インテル® FPGA Power and Thermal Calculator ユーザーガイド改訂履歴

A. 静的消費電力の測定

4.1. インテル® FPGA PTC - Power Summary/Navigation

4.2. インテル® FPGA PTC - 共通のページ要素

4.3. インテル® FPGA PTC - Main ページ

4.4. インテル® FPGA PTC - Logic ページ

4.5. インテル® FPGA PTC - RAM ページ

4.6. インテル® FPGA PTC - DSP ページ

4.7. インテル® FPGA PTC - Clock ページ

4.8. インテル® FPGA PTC - PLL ページ

4.9. インテル® FPGA PTC - I/O ページ

4.10. インテル® FPGA PTC - Transceiver ページ

4.11. インテル® FPGA PTC - HPS ページ

4.12. インテル® FPGA PTC - Crypto ページ

4.13. インテル FPGA PTC - NOC ページ

4.14. インテル® FPGA PTC - HBM ページ

4.15. インテル® FPGA PTC - Thermal ページ

4.16. インテル® FPGA PTC - Report ページ

インテルのみ表示可能 — GUID: ame1670545308787

Ixiasoft

3.4. インテル® FPGA PTC - IP Wizard

インテル® FPGA Power and Thermal Calculator (PTC) の IP Wizard を使用すると、IP ブロックを選択、コンフィグレーション、およびインスタンス化し、そのブロックを現在のデザインに追加することができます。

- IP Wizard は、PTC のファイルメニューから起動することができます。それには、File > IP Wizard をクリックします。または、ツールバーの IP Wizard ボタンをクリックします。

図 21. IP Wizard の起動

図 22. IP Wizard ボタンでの起動

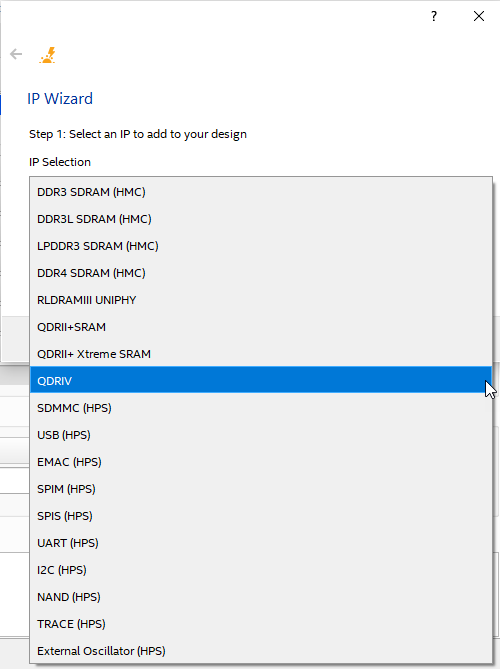

図 22. IP Wizard ボタンでの起動 - IP Wizard の開始ダイアログボックスでは、プルダウンリストから IP を選択するように求められます。デザインに追加する IP を選択し、Next をクリックします。

図 23. IP選択ページ

- IP Wizard は次に、選択している IP をコンフィグレーションするためのダイアログボックスを表示します。適切な情報を入力し、Next をクリックします。

図 24. IP のコンフィグレーション・ページIP のパラメーター・コンフィグレーション・ページーのパラメーターは、選択している IP によって異なります。これらのパラメーターは、IP Catalog ウィザードのパラメーターのサブセットです。各 IP のパラメーターの詳細に関しては、該当する IP ユーザーガイドを参照してください。

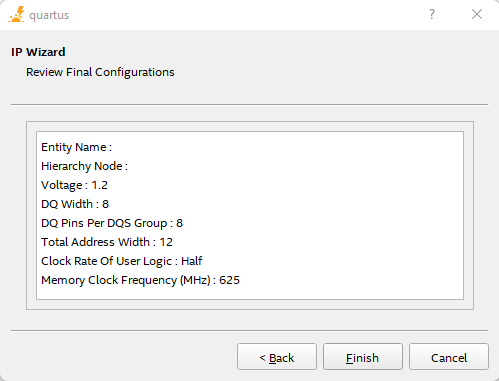

表 8. IP のコンフィグレーション・フィールドこの表は、インテル Stratix 10 デバイスの EMIF IP にのみ関連します。 列の見出し 詳細 Entity Name エンティティーの名前を指定します。 Hierarchy Node IP インスタンスの名前を指定します。 Voltage ペリフェラル・デバイスとインターフェイス間の信号の I/O 電圧を指定します。 Data Width (Bits) 特定の IP のインターフェイス・データ幅 (ビット単位) を指定します。 Data Group Width データグループの幅を指定します。 Memory Device(s) インターフェイスに接続しているメモリーデバイスの数を指定します。 Total Address Width 合計アドレス幅を指定します。この値を使用して、必要なアドレスピンの総数が導出されます。 DDR Rate ユーザーロジックのクロックレートを指定します。メモリークロックの周波数に対するユーザーロジックのクロック周波数を決定します。例えば、FPGA からメモリーデバイスに送信されるメモリークロックが 800MHz でトグルする場合、「クォーターレート」インターフェイスは、FPGA のユーザーロジックが 200MHz で動作することを意味します。 PHY Rate PHY ロジックのクロックレートを指定します。メモリークロックの周波数に対する PHY ロジックのクロック周波数を決定します。例えば、FPGA からメモリーデバイスに送信されるメモリークロックが 800MHz でトグルする場合、「クォーターレート」インターフェイスは、FPGA の PHY ロジックが 200MHz で動作することを意味します。 Memory Clock Frequency (MHz) メモリークロックの周波数を指定します (MHz 単位)。 - IP Wizard は次に、コンフィグレーションの詳細を表示して確認を促します。コンフィグレーションを変更する場合は Back をクリックします。それ以外の場合は、コンフィグレーションに問題がないことを確認して Finish をクリックします。

図 25. IP のコンフィグレーション確認ページ

IP Wizard を終了すると、システムは、追加した IP に応じて新しい行を PTC のページ (Logic、PLL、I/O など) に追加します。