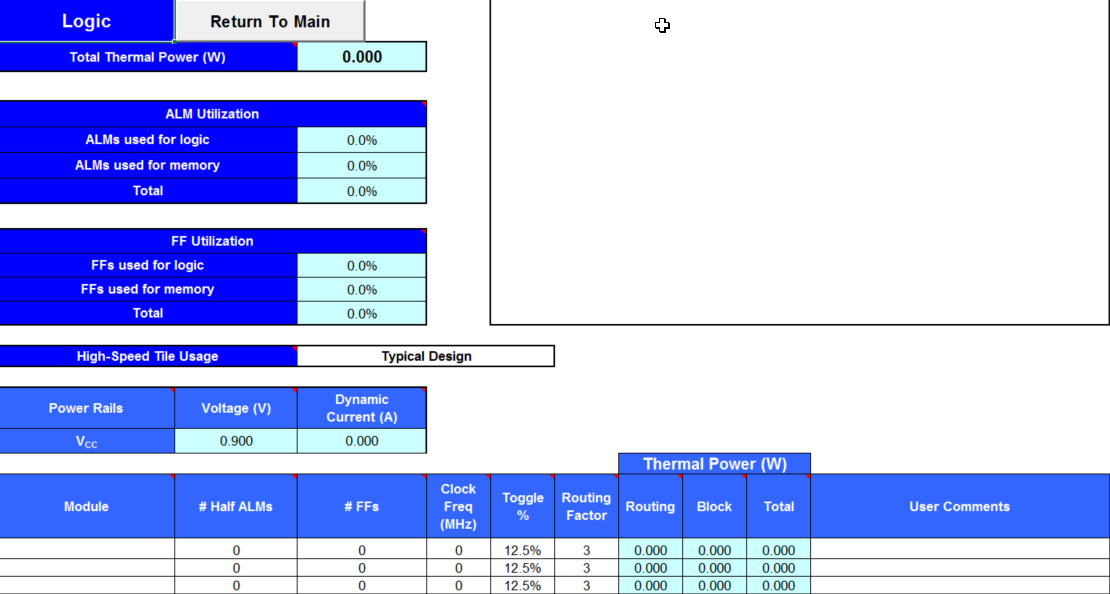

4.3. Cyclone® 10 GXデバイス用 EPE - Logic ワークシート

| 入力パラメーター | 説明 |

|---|---|

| High-Speed Tile Usage | High-Speed Tile Usage の設定を選択します。この値は、Typical Design、Typical High-Performance Design、または Atypical High-Performance Design のいずれかになります。

この設定は、EPE スプレッドシートの Main ワークシートのスタティック消費電力 (PSTATIC) に影響を及ぼします。また、EPE スプレッドシートの Logic ワークシートに入力されたロジックリソースによるダイナミック消費電力にもわずかに影響を与えます。

注: Quartus® Primeソフトウェアからデザインをインポートする際、Early Power Estimator は high-speed tile usage で精密な値をインポートし、この設定値をImportedに変更します。

|

| 入力パラメーター | 説明 |

|---|---|

| Module | デザインの各モジュール名を入力します ( オプション入力 )。 |

| #Half ALMs | デザインで使用されている ALM( アダプティブ・ロジック・モジュール ) の数を2倍入力します。 |

| # FFs | このモジュールの FF( フリップフロップ ) の数を入力します。 FF に関連付くクロックの配線消費電力は、EPE スプレッドシートの Clock ワークシートで個別に計算されます。 |

| Clock Freq (MHz) | クロック周波数を単位 MHz で入力します。この値は、デバイスファミリーのより大きい周波数仕様により制限されます。

注:

Quartus® Primeソフトウェアからデザインをインポートする際、一部のインポートされた ALM の半分と FF は、クロック周波数が0MHz の可能性があり、これは、次の2つの理由のいずれかにより発生します。

|

| Toggle % | ブロック出力信号が値を変える際に、クロックサイクルの平均割合を入力します。トグルレートは、クロック周波数で乗算され、1秒あたりの遷移数を決定します。例えば、トグルレート 12.5% で 100 MHz の周波数の場合、各 LUT または FF の出力トグルは1秒あたり 1,250 万回 (100MHz × 12.5%) になります。 トグルレートの幅は、0~100% です。一般的に、トグルレートは 12.5% で、これは 16 ビット・カウンターのトグルレートです。たいていのロジックは頻繁にはトグルしないため、トグルレートは 50% 未満が現実的です。トグルレートを低く見積らないよう、シミュレーションで得た現実的なトグルレートを使用してください。 例えば、入力が VCC に接続された TFF(T フリップフロップ ) は、クロックサイクルごとに出力がロジック状態を変化させるため、トグルレートは 100% です。より詳しい解析について、下の図で示す4ビット・カウンターの例を参照してください。 FF を含むいずれの行でも、トグルレートは 100% 以上にできません。デザイン中のわずかな ALM ではグリッチが起こるかもしれず、そのような ALM ではトグルレートが 100% を超える場合があります。このような ALM は # FFs を 0 に設定して個別の行に入力します。 |

| Routing Factor | 出力の配線消費電力の範囲を示します。 電力の影響が大きく、この要因によりキャプチャーされる特性には、次のものがあります。

このフィールドのデフォルト値は、標準です。実際の値は、デザインのブロック間、およびデザインの配置により異なります。より正確な結果は、 Quartus® Primeソフトウェアが配置情報の詳細にアクセスできるため、 Quartus® Primeソフトウェアからこの値をインポートする必要があります。 Quartus® Primeデザインが存在しない場合、通常、より高い値は FPGA 上の広い距離で多数の目的地にファンアウトする信号に対応し、同時に低い値はより局在化の信号に対応します。 このフィールドをデフォルト値から変更し、ブロックの配置に応じて消費電力の変動を調べることができます。この値を変更する際は、標準デザインで極端な値をなるべく使用せず、デザインの小さなサブセットに対してのみに使用するように留意してください。 |

| Thermal Power (W) - Routing | 配線見積りに起因する消費電力を単位 W で示します。 配線消費電力は、配置配線によって異なり、デザインの複雑さに関係します。ここに示された値は、100 以上の実際のデザインでの観測に基づいた配線消費電力を表しています。 デザインで使用された正確な配線に基づく正確な解析には、 Quartus® Prime Power Analyzer を使用します。 |

| Thermal Power (W) - Block | ALM の内部トグルに起因する消費電力を単位 W で示します。 ロジックブロック消費電力は、実装された機能と各種入力の相対的なトグルレートの組み合わせです。EPE スプレッドシートでは、100 以上の実際のデザインで観測した動作に基づく見積りを使用します。 デザインの正確な合成に基づく正確な解析には、 Quartus® Prime Power Analyzer を使用します。 |

| Thermal Power (W) - Total | EPE スプレッドシートに入力された情報に基づいた消費電力の見積りを単位 W で示します。これは、配線消費電力とブロック消費電力の合計と同じです。 |

| User Comments | コメントを入力します ( オプション入力 )。 |

最初の TFF のcout0出力は、クロックサイクルごとに信号がトグルするため、トグルレートは 100% です。2番目の TFF のcout1出力は、出力が2クロックサイクルごとにトグルするため、トグルレートは 50% です。同様に、出力cout2とcout3のトグルレートは、それぞれ 25% と 12.5% です。したがって、この4ビット・カウンターの平均トグルレートは、(100 + 50 + 25 + 12.5)/4 = 46.875% になります。

ロジック・アレイ・ブロックのコンフィグレーションについて詳しくは、 Cyclone® 10 GX Device Handbook のLogic Array Blocks and Adaptive Logic Modules の章を参照してください。