エグゼクティブ・サマリー

エグゼクティブ・サマリー

LLT やその他の時間に依存するアプリケーションは、FPGA アクセラレーションにとって最適なユースケースです。この市場のニーズに応えるため、Flyslice Technologies は、FPGA ベースのアクセラレーション・カードである FA728Q を開発しました。FA728Q アクセラレーション・プラットフォームは、パワフルな FPGA リソース、豊富なストレージ容量、エンドユーザー向けの使いやすいインターフェイスを有しています。アクセラレーション・ボードの開発を促進、簡素化、標準化するために、Flyslice Technologies は OFS インフラストラクチャーを活用しています。これは、「テイク・アンド・テイラー」アプローチを駆使して FPGA ソリューションの迅速な開発を行うための、強力なメソッドを提供するものです。Flyslice Technologies は、TCP/IPOFS インフラストラクチャーを使用して、、TCP/IP オフロード・エンジンを、一般に FPGA 「シェル」と呼ばれるオープンソースのベース FIM に統合します。

背景と課題

LLT は、注文入力と注文実行の間の時間遅延を最小限に抑え、金融証券の取引を電子的に実行する現代的な手法です。大規模な投資銀行、ヘッジファンド、その他の金融機関では、一般的にこの方法を使用しています。過去には、取引は電子的ではなく手動で実行され、取引の実行は数秒から数分までの幅がありました。しかし、ハードウェアとそれに対応するソフトウェアの技術的進歩により、特定の市場のシグナルと動きに基づいて、自動的に売買の決定を行うようにシステムをプログラムすることができ、取引実行時間はミリ秒単位に短縮されました。近年、FPGA ベースのアクセラレーション製品が幅広く利用できるようになったことで、取引時間はさらにマイクロ秒またはサブマイクロ秒に短縮されています。

それと同時に、LLT システムは、オーダーブックとのやり取りのために、各取引会社の特定の取引戦略が固有にもつ、複雑な取引アルゴリズム・モデルにますます依存しています。ソリューションには、ヘテロジニアス・コンピューティングなど、取引会社の電力とパフォーマンス要件を満たすために、汎用プロセッサーと専用コプロセッサー・コンピューティングが必要です。FPGA は、カスタマイズされた取引アルゴリズムの実装に最適です。しかしながら、このハードウェア・アクセラレーション・デバイスのプログラミングには時間がかかることがあり、FPGA ファミリーが改善、進化するにつれて移行が難しくなる可能性があります。

中国に本社を置く企業 Flyslice Technologies は、LLT セグメントを含むデータセンターにおけるヘテロジニアス・アクセラレーションとハイパフォーマンス・コンピューティングの需要に対応するため、積極的に取り組んでいます。同社は FPGA ベースのハードウェア・アクセラレーター・プラットフォーム、FPGA アクセラレーション・知的財産 (IP) 機能、FPGA ベースのプラットフォーム・デザイン・サービスなどを市場に投入しています。

ソリューション

LLT アプリケーションの低レイテンシー、標準化、移植性の要件を満たすため、Flyslice Technologies は、インテグレーテッド TCP/IP オフロード・エンジンをインスタンス化する FA728Q アクセラレーション・カードを開発しました。この実現のため、Flyslice Technologies は、OFS のオープンソース・リリースで提供されているベース FIM を元に修正を加えました。再構成可能なアーキテクチャーと「テイク・アンド・テイラー」アプローチのおかげで、OFS により OFS ソフトウェア・ドライバーやライブラリーなど、提供されるインフラストラクチャーを活用しつつ、アルゴリズムを FA728Q アクセラレーション・カードに移植できるようになり、変更が最小限となりました。

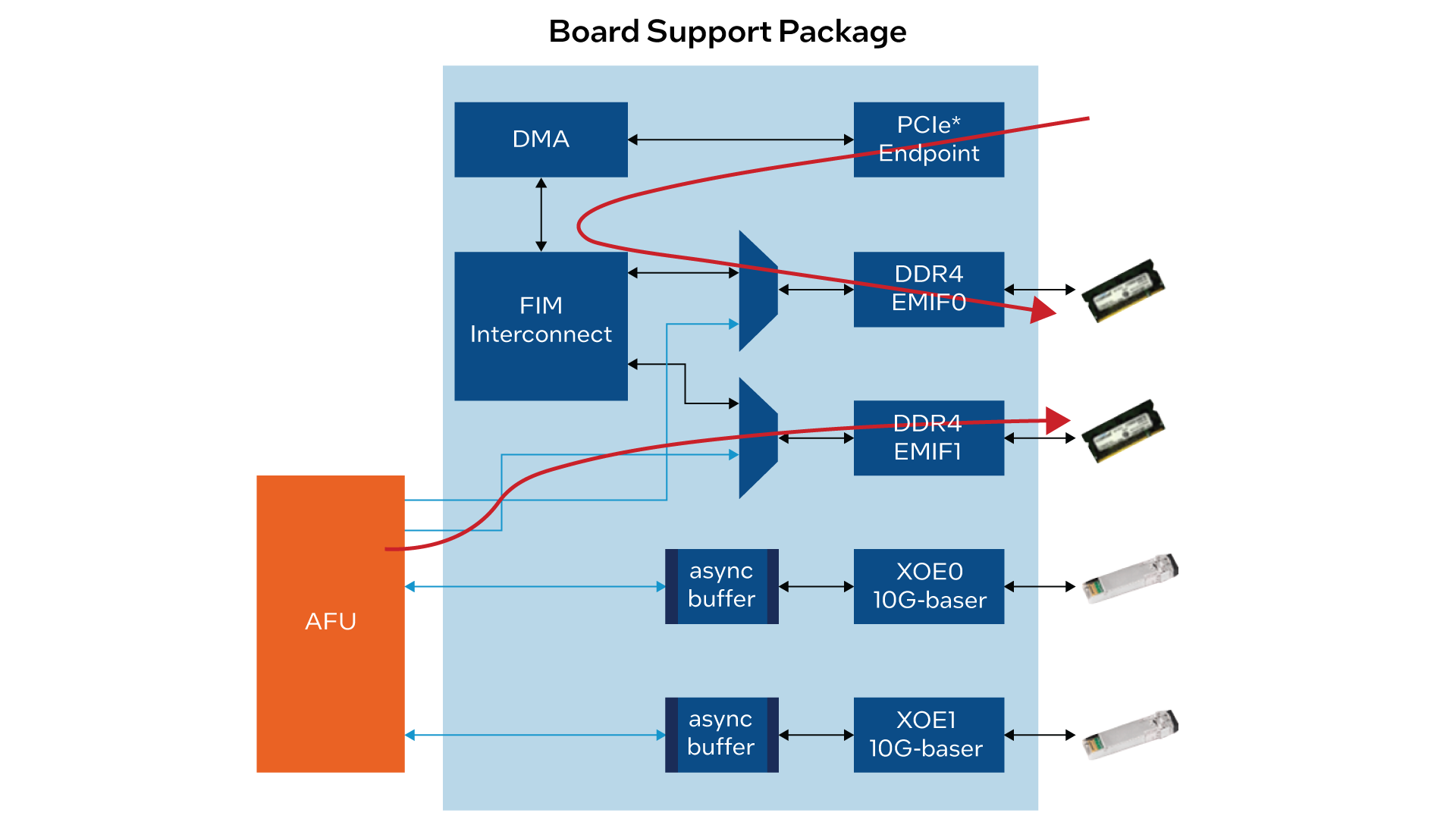

OFS は、カスタムの FPGA ベースのボードやワークロード開発を迅速化するために必要なすべての主要なデザイン、ソフトウェア、インフラストラクチャー・コンポーネントを提供する、オープンソースのハードウェアとソフトウェアのインフラストラクチャーです。OFS インフラストラクチャーは、一般に「シェル」と呼ばれる FIM、およびワークロード開発用に指定されたリージョンであるアクセラレーター・ファンクショナル・ユニット (AFU) リージョンで構成されています。OFS を使用すれば、FPGA ボードまたは FIM 開発者は、オープンソースのインフラストラクチャーまたはベースの FIM を活用し、ターゲットとなるアプリケーションまたは業界に応じてそのボード用に調整されたカスタム FIM を迅速に開発できます。OFS にはまた、oneAPI Accelerator Support Package (ASP) も搭載されており、FPGA ハードウェアとデザインフローを抽象化するために活用できます。OFS は、開発者の時間を節約し、FPGA 世代全体の移植性を向上させ、業界標準インターフェイスを使用し、oneAPI を使用した任意の高レベル・デザイン・フローを実現します。

FA728Q アクセラレーション・カードは、現在入手可能で、インターフェイスごとに最大 100GbE をサポートする、32GB のオンボード DDR4 メモリーと 3 つの QSFP28 ソケットを提供するハイエンド PCIe ベースの FPGA アクセラレーション・ボードです。FA728Q アクセラレーション・カードは OFS インフラストラクチャーを通じて oneAPI でも使用できるため、顧客はカーネルを RTL で実装したり、CPU/GPU から C/C++ などの高レベル設計言語にアルゴリズムを移行したりできます。インテル® oneAPI ベース・ツールキットは、カーネルの FPGA リソースへの統合と最適化にも役立ち、市場投入までの時間をさらに改善させます。

Flyslice Technologies は、インテル® Agilex™ 7 FPGA I シリーズを使用した FA927S カード、インテル® Agilex™ FPGA F シリーズを使用した FA925E カードなど、インテル® Agilex™ FPGA 搭載ボードの開発も開始しています。

FA927S カードは、最大 116Gbps の高いトランシーバー・レートを備え、PCIe 5.0 x16、Compute Express Link (CXL) をサポートしています。帯域幅負荷の高いアプリケーションを対象とし、現在は RTL ベースの開発で利用可能です。FA927S カードは、2024年第1四半期に OFS をサポートします。

一方、FA925E カードは、8GB の 4 つのバンクと 4GB DDR4 の 4 つのバンクを搭載し、合計 48GB のオンボードメモリーを備えています。外部メモリー容量と帯域幅要件の高いアプリケーション向けに設計されています。このカードは OFS を完全にサポートし、2023年末までに発売されます。 3 つのアクセラレーション・カードを比較するには、表 1. を参照してください。

表 1.比較表

|

|

|

|

|

|---|---|---|---|

| 電源 | 215W | 200 W | 150 W |

| 冷却要件 | アクティブ/パッシブ (オプション) | アクティブ/パッシブ (オプション) | アクティブ/パッシブ (オプション) |

| フォームファクター | 3/4 レングス、フルハイト、デュアルスロット PCIe | ハーフレングス、フルハイト、デュアルスロット PCIe | 3/4 レングス、フルハイト、デュアルスロット PCIe |

| ネットワーク・インターフェイス | トリプル QSFP28 ポート: 3 x 100GbE / 40GbE | デュアル QSFP28 ポート: 2 x 100GbE / 40GbE | デュアル QSFP28 ポート 2 x 100GbE / 40GbE |

| メモリー・インターフェイス | 4 x 8GB DDR4、ECC 搭載 2,400MHz | 4 x 8GB DDR4、ECC 搭載 2,400MHz | 4 x 8GB および 4 x 4GB DDR4、ECC 搭載 2,400MHz |

| PCIe インターフェイス | - | 5.0 x16 | - |

| 拡張インターフェイス | - | PCIe 4.0 拡張機能向け x8 スリム SAS コネクター 2 個 | - |

| 管理ポート | マイクロ USB | マイクロ USB | マイクロ USB |

| FPGA デバイス | 1SX280HN2F43E2VG | AGIB027R29A1E2VR3 | AGFB027R25A2E2V |

検索結果

FA728Q カードに Flyslice Technologies が実装したオフロード・エンジン IP 機能は、LLT 要件を満たすために、レイテンシーとパフォーマンスに最適化されています。高速化モードでは、TCP 送信レイテンシーが 100ns 未満で、タイムクリティカルなネットワーク・アプリケーション向けに安定な低レイテンシー接続を実現します。表 2. では、さまざまな接続の測定レイテンシーを示しています。表 3. では、高帯域幅 PCIe 3.0 x16 および DDR インターフェイスを示しています。

| 仕様 | 価値 |

|---|---|

| 最大 TCP/UDP 接続数 | TCP: 63、UDP: 63 |

| TCP TX レイテンシー (高速化モード) | 15 クロック |

| TCP TX レイテンシー (非高速化モード) | 46 クロック |

| TCP RX レイテンシー | 32 クロック |

| UDP TX レイテンシー | 512 バイトパケット: 42 クロック、128 バイトパケット: 18 クロック |

| UDP RX レイテンシー | 23 クロック |

| oneAPI カーネルのループバック・レイテンシー | 18 クロック |

表2.TCP/IP オフロード・エンジン (TOE) 仕様

注意:

1.1 クロック期間は 6.4ns です

2.TX レイテンシーは、パケット EOP の立ち下がりエッジから XGMII TXC の有効なデータにカウントされます

3.RX レイテンシーは、パケット SOP から XGMII RXC の有効なデータにカウントされます

| データパス | 帯域幅 |

|---|---|

| ホスト書き込みメモリー | 8,192KB ブロックに対して 8,287.6MBps |

| ホスト読み取りメモリー | 8,192KB ブロックに対して 8,241.19MBps |

| カーネル書き込みメモリー | 4,096MB ブロックに対して 16,909.6MBps |

| カーネル読み取りメモリー | 4,096MB ブロックに対して 17,340.3MBps |

表3.各インターフェイスが提供する帯域幅

OFS により、ソフトウェアの API ドライバーから基礎となるハードウェアまで、顧客に必要なアクセラレーション・プラットフォームを一連の機器として、より簡単かつ迅速に構築できるようになりました。

OFS を使用した FPGA アクセラレーションの開始方法

FPGA 開発者は、FA728Q アクセラレーター・カードおよび OFS 対応ボードを活用し、オープンソースのドキュメントとソースコードを使用して、カスタム・ワークロードの構築を開始できます。

次の表は、開発者が Flyslice Technologies のアクセラレーション・ボードを使用して、FPGA ベースのワークロード開発に取りかかる方法を概説したものです。

| ワークロード向けに FPGA アクセラレーションを活用 | |

|---|---|

| ステップ 1: ボードを選択する | Flyslice Technologies の OFS 対応ボード、FA728Q アクセラレーター・カードをご覧ください |

| ステップ 2: OFS オープンソース・リソースを評価する |

Flyslice Technologies が、該当するバージョンの OFS の技術資料を提供します。 |

| ステップ 3: オープンソース・ハードウェアおよびソフトウェア・コードにアクセス |

Flyslice Technologies が、該当する OFS ソフトウェアおよびハードウェア・コードを提供します。これは、インテルが提供する OFS ベースコードの、Flyslice Technologies 独自のディストリビューションです。 |

| ステップ 4: RTL または C/C++ を使用したワークロードを開発 (oneAPI を使用) |

OFS RTL フローに従う、 または OFS が oneAPI カーネルのコンパイルを可能にします。oneAPI 開発フローを使用して、FPGA ワークロードを C/C++ で構築します。 |