2021年12月11日に米国で発表された資料の抄訳です。最新情報:インテル コーポ―レーションは、ムーアの法則の継続に向けた絶え間ない取り組みの一環として、コンピューティングを次の10年に向けて進歩、加速させる基盤となるパッケージング、トランジスター、量子物理学での画期的な最新技術を公開しました。半導体のデバイス技術とプロセス技術に関する国際会議 IEEE International Electron Devices Meeting(IEDM)2021で、ハイブリッド・ボンディング接続により 10倍以上のインターコネクト密度を実現するパッケージング技術、トランジスター・スケーリングでの面積効率30%~50%の向上、電力とメモリーの最新技術における大幅な進歩、そして今後のコンピューティングに革新をもたらす可能性を秘める物理学における新たなコンセプトについて説明しました。

インテル コーポレーション シニアフェロー 兼 コンポーネント・リサーチ・グループ ゼネラル・マネージャーであるロバート・チョウ(Robert Chau)は「インテルは、ムーアの法則を前進させるために必要な研究とイノベーションを決して止めません。IEDM 2021において、インテルのコンポーネント・リサーチ・グループは、この業界と社会が求める強力なコンピューティングへの飽くなきニーズに応えるために、必要な革新的なプロセス技術とパッケージング技術での研究で重要、かつ飛躍的な進展をお伝えしました。これは、ムーアの法則を前進させるためにイノベーションの最前線に立ち続けているインテル最高峰の科学者とエンジニアによる絶え間ない努力の成果です」と述べました。

重要な理由:メインフレームからスマートフォンまで、テクノロジーのあらゆる世代におけるニーズを満たす上で、ムーアの法則は数々のコンピューティング・イノベーションを残してきました。無限に増大するデータとAIが主導するコンピューティング新時代へと移行しつつある現在も、この進歩は続いています。

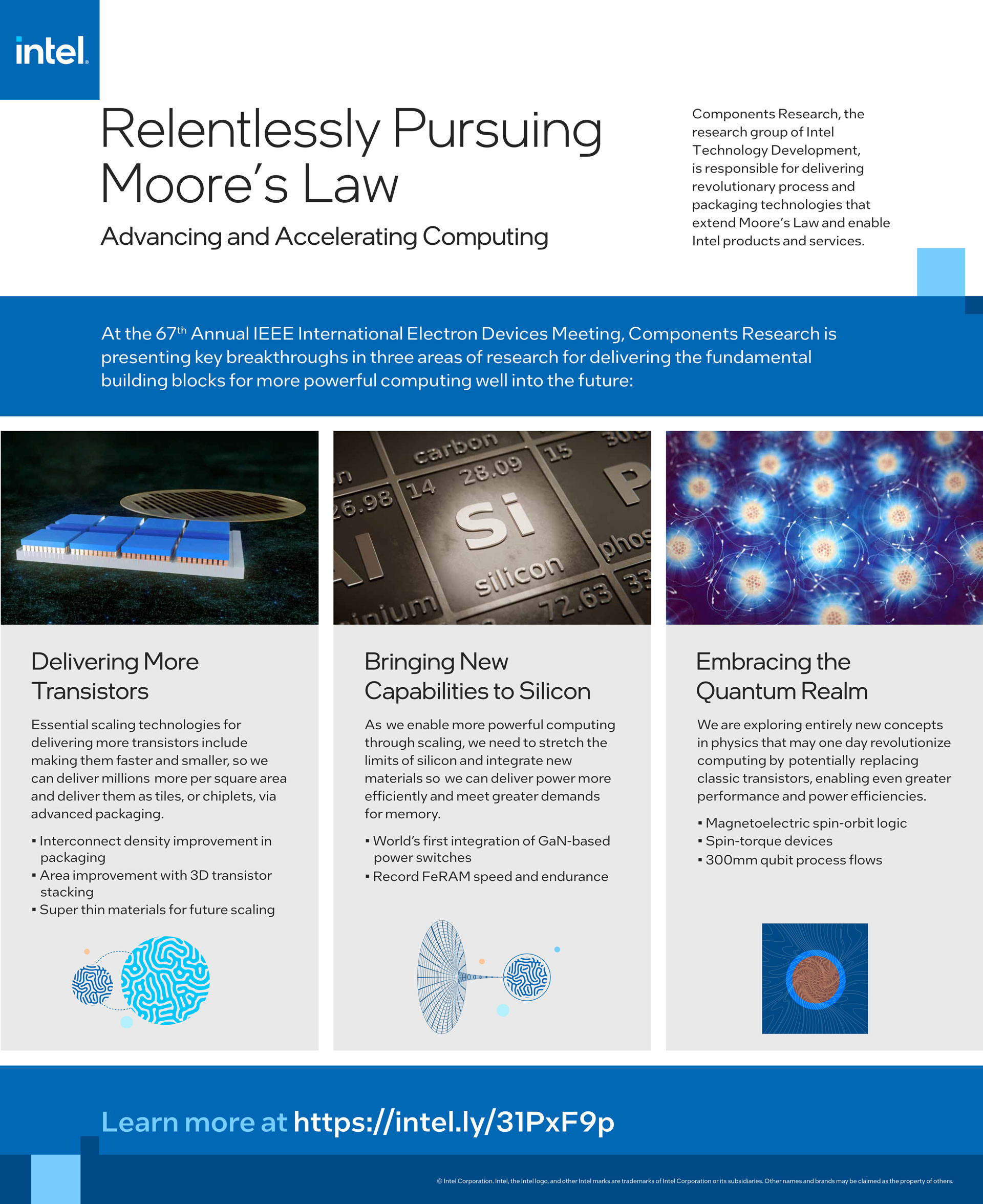

ムーアの法則の基盤は、継続的なイノベーションです。インテルのコンポーネント・リサーチ・グループは、イノベーションを起こすために次の3つの主要領域に取り組んでいます。それは、トランジスター数増大の根幹を支えるスケーリング技術、電力効率とメモリー容量を拡大させる新たなシリコン機能、そして世界のコンピューティングに革新をもたらす物理学での新たなコンセプトの探究です。これまでムーアの法則の壁を打ち破りイノベーションを起こしてきた現在の製品に実装されている画期的な技術の多くは、コンポーネント・リサーチの研究活動から始まっています。これには歪みシリコン、Hi-K メタルゲート、FinFET トランジスター、RibbonFET、そして EMIBやFoveros Directなど、パッケージング技術のイノベーションも含まれています。

実現までの過程:IEDM 2021で今週公開された画期的な技術は、インテルが最先端の3つの領域を通じて、2025年とその先までムーアの法則を引き続き前進させ、そのメリットを応用できることを示しています。

- インテルでは、今後リリースする製品でのトランジスター数のさらなる増大を目指し、根幹を支えるスケーリング技術の重要な研究を進めています。

- インテルの研究者は、ハイブリッド・ボンディング接続の設計、プロセス、組み立てに関する課題を解決するソリューションの要点をまとめました。パッケージングで10倍以上のインターコネクト密度が想定されています。また、インテルは7月に開催したIntel Acceleratedイベントで、10ミクロン未満のバンプピッチを実現し、3Dスタッキングのインターコネクト密度を1桁高めるFoveros Directを導入する計画を発表しました。インテルは、エコシステムとして進化したパッケージング技術のメリットを最大限に活かしながら、ハイブリッド・ボンディング接続のチップレットの提供を目指し、新たな業界標準とテスト手順の確立を呼びかけています。

- インテルでは、全周ゲート型(GAA)RibbonFETの先を見据え、ポストFinFET時代の到来に向けた複数のトランジスターを積層する(CMOS)アプローチにより、1平方ミリメートル当たりのトランジスター数を増大させ、ムーアの法則の継続させるロジック・スケーリングの最大30%~50%の進展を目指しています。

- インテルはまた、ダイ面積当たりのトランジスター数を数百万単位で増大させ、次の10年でこれまで以上に強力なコンピューティングを実現する従来のシリコンチャネル数の限界を超えたトランジスターの製造に取り組んでいます。そして、原子わずか数個分ほどの厚みしかない新素材の使用方法や、その仕組みを示す先進的な研究を通じて、オングストローム時代に向けてムーアの法則を前進させるための道を拓いています。

- インテルは次のとおり、シリコンに新たな機能をもたらしています。

- 300mmのウエハー上に実装されたシリコンベースのCMOSに世界で初めて窒素ガリウム(GaN)ベースの電源スイッチを内蔵し、電力効率を向上させる技術を実現しました。これにより、CPUへの低損失かつ高速の電力供給を実現する準備が整うと同時に、マザーボードのコンポーネント数の削減によりスペースの縮小にもつながります。

- もう1つの進歩は、ゲームからAIまで、ますます複雑化するコンピューティング・アプリケーションに対応できるメモリーリソースの拡張による、次世代の組込みDRAM技術の可能性を示す新しい強誘電体素材を使用した業界をリードする低レイテンシーの読み込み/書き込み性能です。

- インテルは、シリコン製トランジスターを基盤とする量子コンピューティングにおいて圧倒的なパフォーマンスとともに、室温で動作するデバイスで電力効率の極めて高いコンピューティングを実現する全く新しいスイッチを追求しています。物理学としてこれまでにないコンセプトに基づく革新的技術が、将来的に従来のMOSFETトランジスターに取って代わる可能性もあります。

- IEDM 2021 でインテルは、室温で動作する世界初の実験的な磁電スピン軌道(MESO)ロジックデバイスを実証しました。これは、ナノスケールの磁気スイッチングに基づく新たな種類のトランジスターを製造できる可能性を示すものです。

- インテルと IMECは、デバイス統合の研究を完全に機能するスピントロニクス・デバイスの実現に近づけるべくスピントロニクス素材の研究を進めています。

- インテルはさらに、CMOS製造技術との互換性を備えるとともに今後の研究が段階を特定されている拡張可能な量子コンピューティングを実現する完全な300mm量子ビットのプロセスフローを公開しました。

コンポーネント・リサーチ・グループについて:インテルのテクノロジー開発部門に属する研究グループであるコンポーネント・リサーチは、ムーアの法則を持続させ、インテルの製品とサービスを生み出す、革新的なプロセス技術とパッケージング技術の選択肢を提供する役割を担っています。未来のニーズを予測する社内の事業部門との連携や、米国政府機関の研究ラボから業界のコンソーシアム、大学の研究チーム、サプライヤーに至る外部機関との協働によって、インテルの研究開発パイプラインが最大限に活かされるように努めています。