インテル® Quartus® Prime 開発ソフトウェア・プロ・エディション v21.4 の問題により、FGT または FHT トランシーバーを含む F タイル PMA/FEC Direct PHY インテル® FPGA IPデザインで、ソフト・リセット・コントローラー (SRC) に関連するタイミングエラーが正しく表示されない可能性があります。

これらのタイミング失敗の特性は、ローンチクロックまたはラッチクロックが src_divided_osc_clkとしてリストされることです。 もう 1 つのクロック (ラッチクロックまたはローンチクロックのいずれか) は、別のクロックになります。

また、報告されるスラックが -90ns のオーダーで非常に大きな負の数であることが分かるかも知れません。

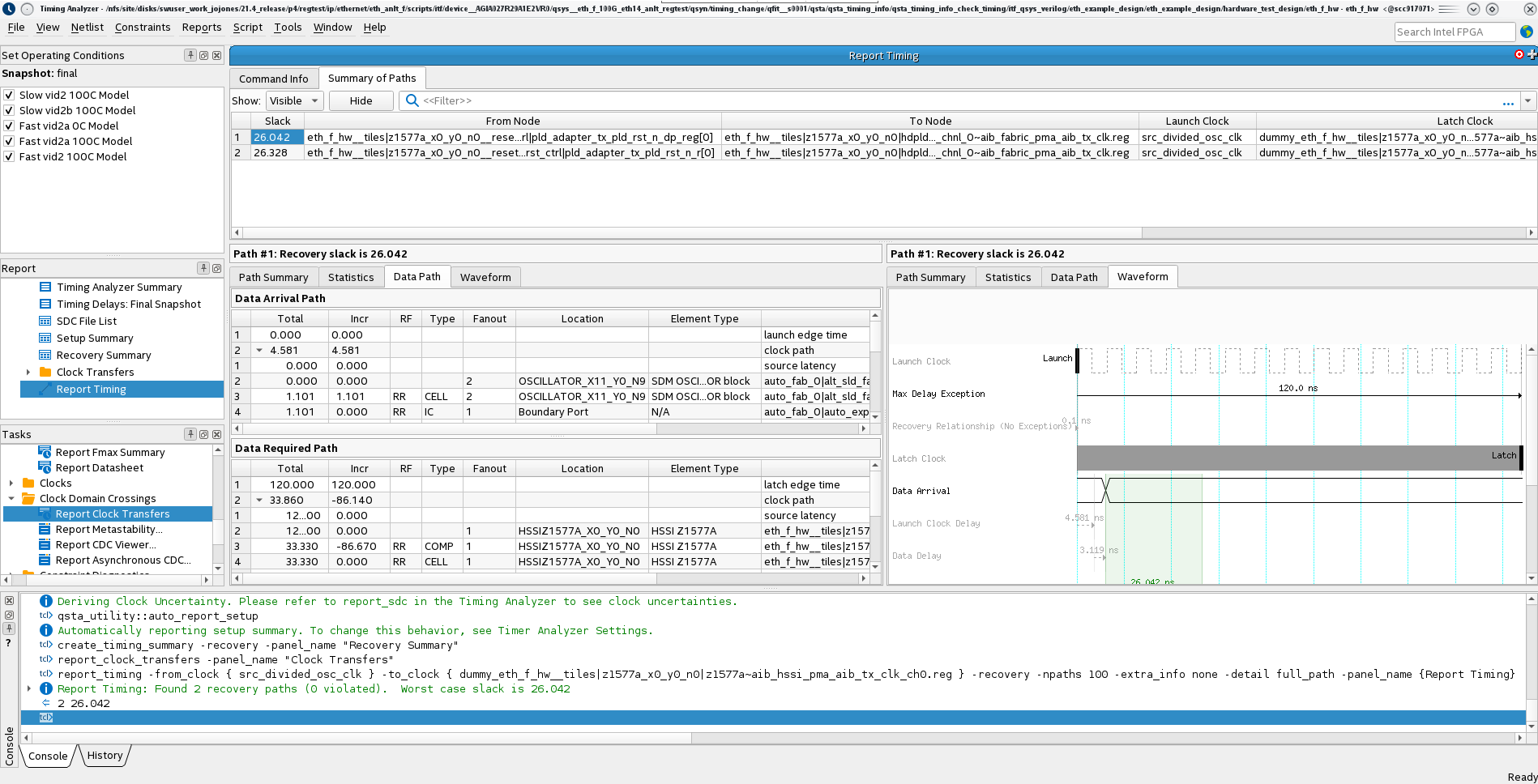

これらのタイミングエラーの例は、次のとおりです。

タイミング失敗例 1

ノードから: IP_INST[0].hw_ip_top|dut|eth_f_0|sip_inst|sip_freeze_tx_src_reg[0]

ノードへのeth_f_hw__tiles|z1577a_x0_y0_n0__reset_controller|x_f_tile_soft_reset_ctlr_sip_v1|x_ftile_reset|rst_ctrl_sync|sip_freeze_tx_SRC_sequence_inst[18]|din_s1

起動クロック: reconfig_clk

ラッチクロック: src_divided_osc_clk

遅延モデル:2_slow_vid2_100cセットアップ:-1.474ホールド:0.027

遅延モデル:2_slow_vid2b_100c設定:-1.574ホールド:0.167

遅延モデル:MIN_fast_vid2a_0c設定:-1.193ホールド:0.216

遅延モデル:MIN_fast_vid2a_100cセットアップ:-1.304ホールド:0.186

遅延モデル:MIN_fast_vid2_100c設定:-1.244ホールド:0.093

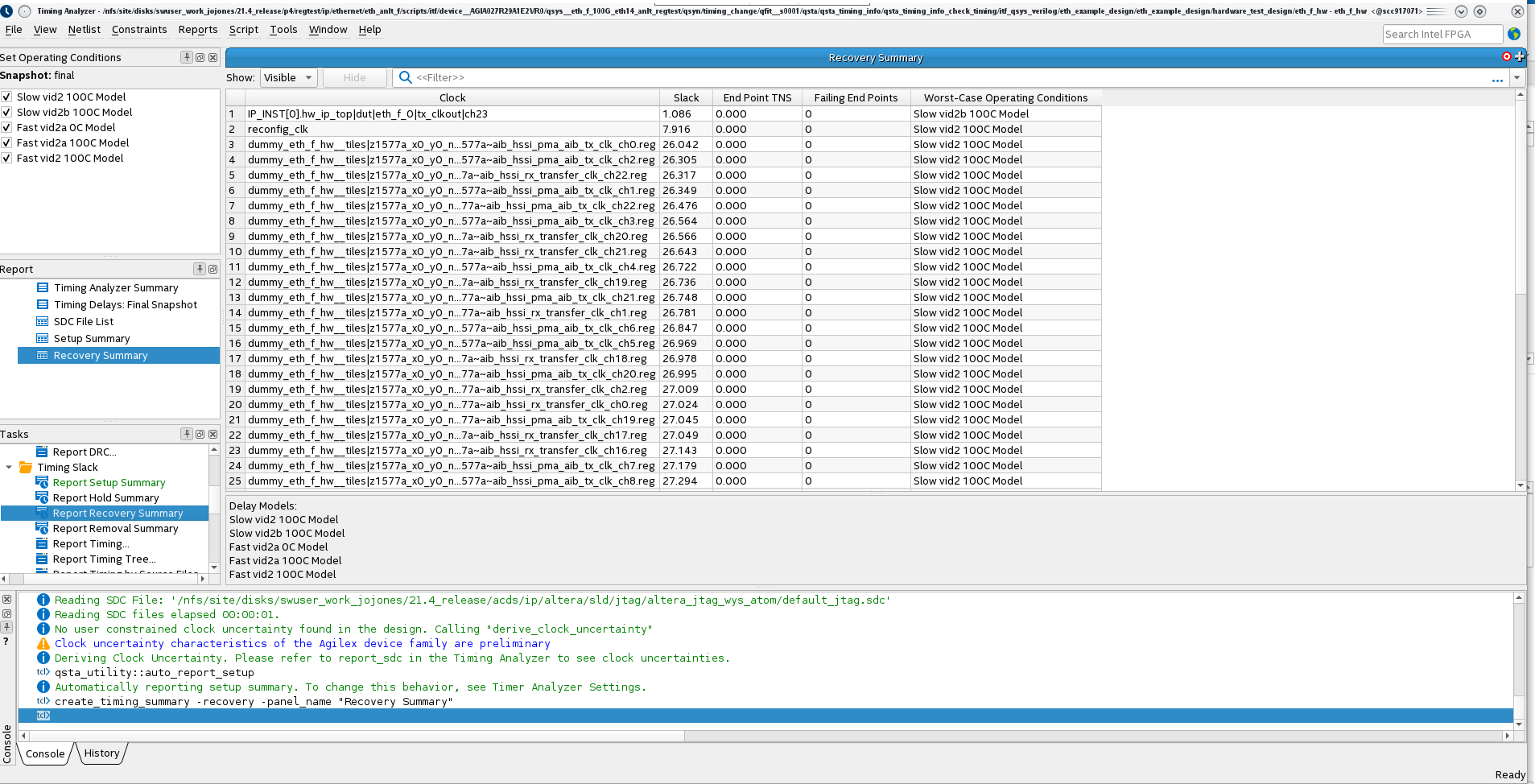

タイミング失敗例 2

ノードから: eth_f_hw__tiles|z1577a_x0_y0_n0__reset_controller|x_f_tile_soft_reset_ctlr_sip_v1|x_ftile_reset|rst_ctrl|dp_sip_rx_aib_control_select[19]

ノードへ: eth_f_hw__tiles|z1577a_x0_y0_n0|hdpldadapt_rx_chnl_19~pld_rx_clk1_dcm.reg

起動クロック: src_divided_osc_clk

ラッチクロック: IP_INST[0].hw_ip_top|clkdiv2_pll_inst|altera_iopll_0_outclk0

遅延モデル:2_slow_vid2_100c復旧:-90.597削除:0.244

遅延モデル:2_slow_vid2b_100c復旧:-90.756削除:0.446

遅延モデル:MIN_fast_vid2a_0c復旧:-90.063削除:0.535

遅延モデル:MIN_fast_vid2a_100c復旧:-90.241除去:0.316

遅延モデル:MIN_fast_vid2_100cリカバリー:-90.057削除:0.076

この問題は、インテル® Quartus® Prime 開発ソフトウェア・プロ・エディション v22.1 から修正されています。

インテル® Quartus® Prime 開発ソフトウェア・プロ・エディション・バージョン 21.4 以前のこの問題を回避するには、ソフト・リセット・コントローラーに関連する失敗したパスは無視しても問題ありません。

ただし、これらの誤ったタイミングエラーを報告しないように修正することを選択した場合は、以下の手順に従ってください。

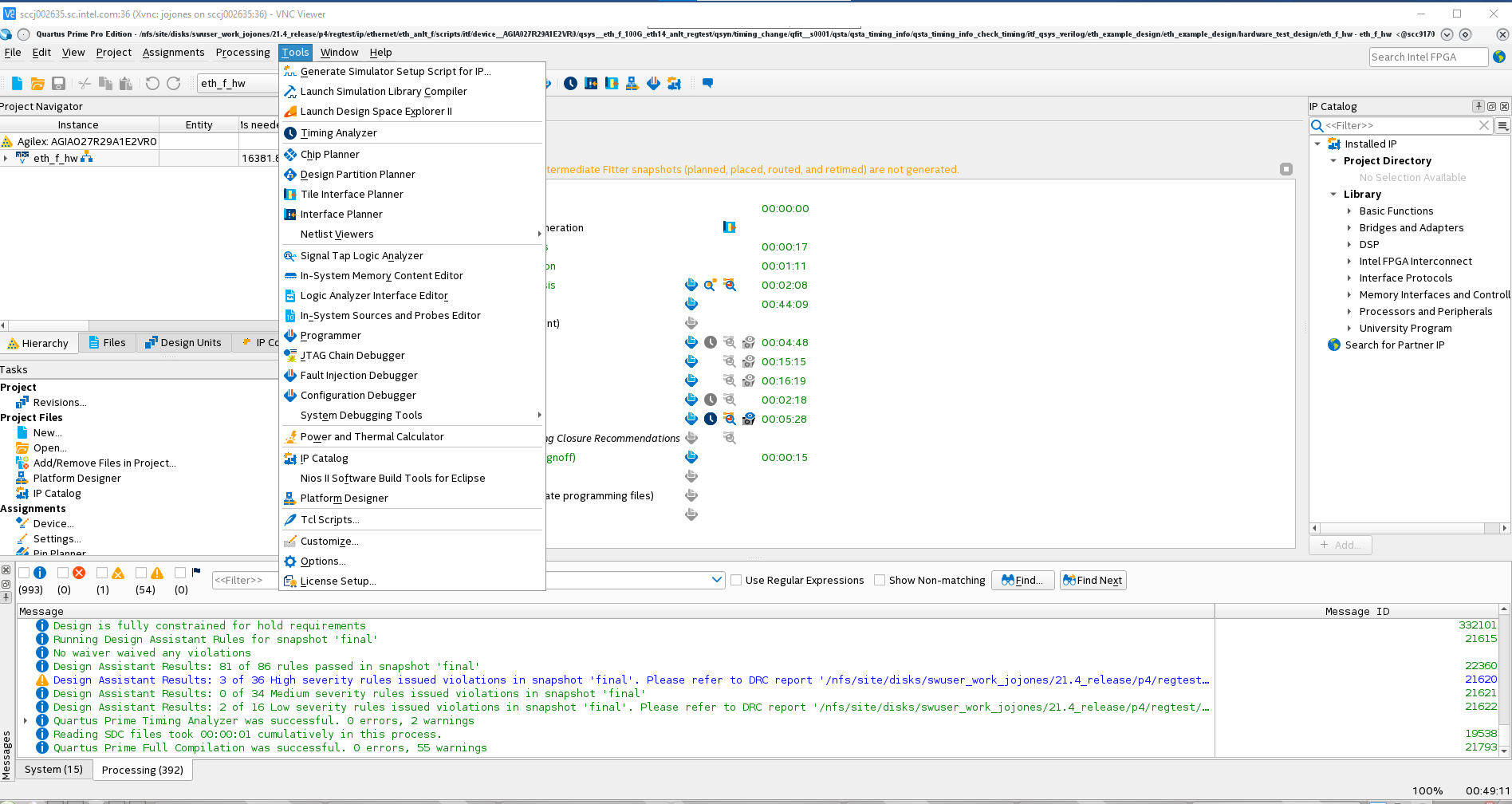

- ) インテル® Quartus® Prime ソフトウェアでデザインをコンパイルしたら、[ツール] メニューからタイミング・アナライザーを起動します。

- ) タイミング・アナライザーがタイミング・ネットリストを作成した後、 生成 セットアップ・タイミング・レポートやリカバリー・タイミング・レポートなど、さまざまなタイミングレポートに対応します。

この場合、フォルスパスが制約されていない場合でも、タイミング・アナライザーはタイミングエラーを報告しません。

-

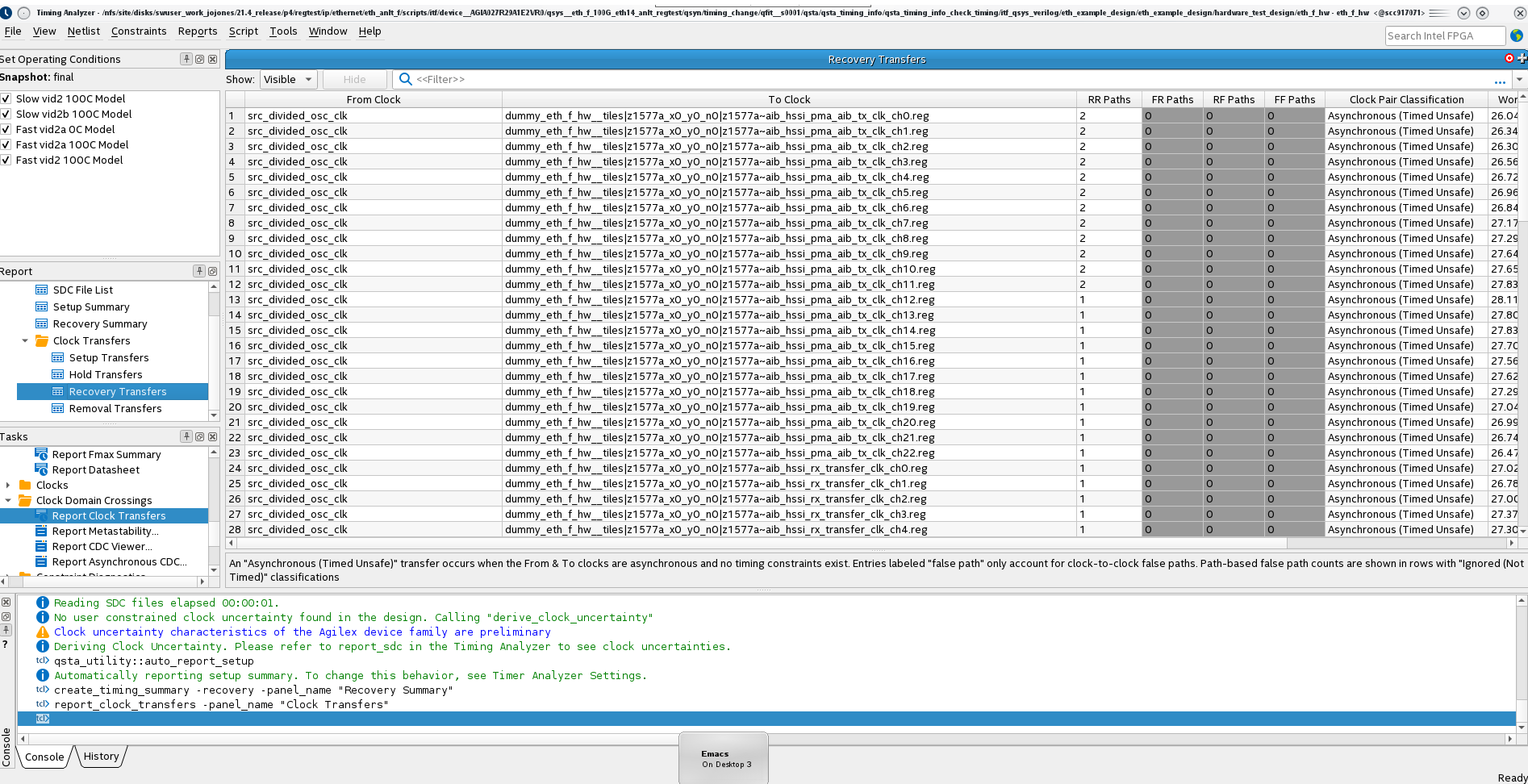

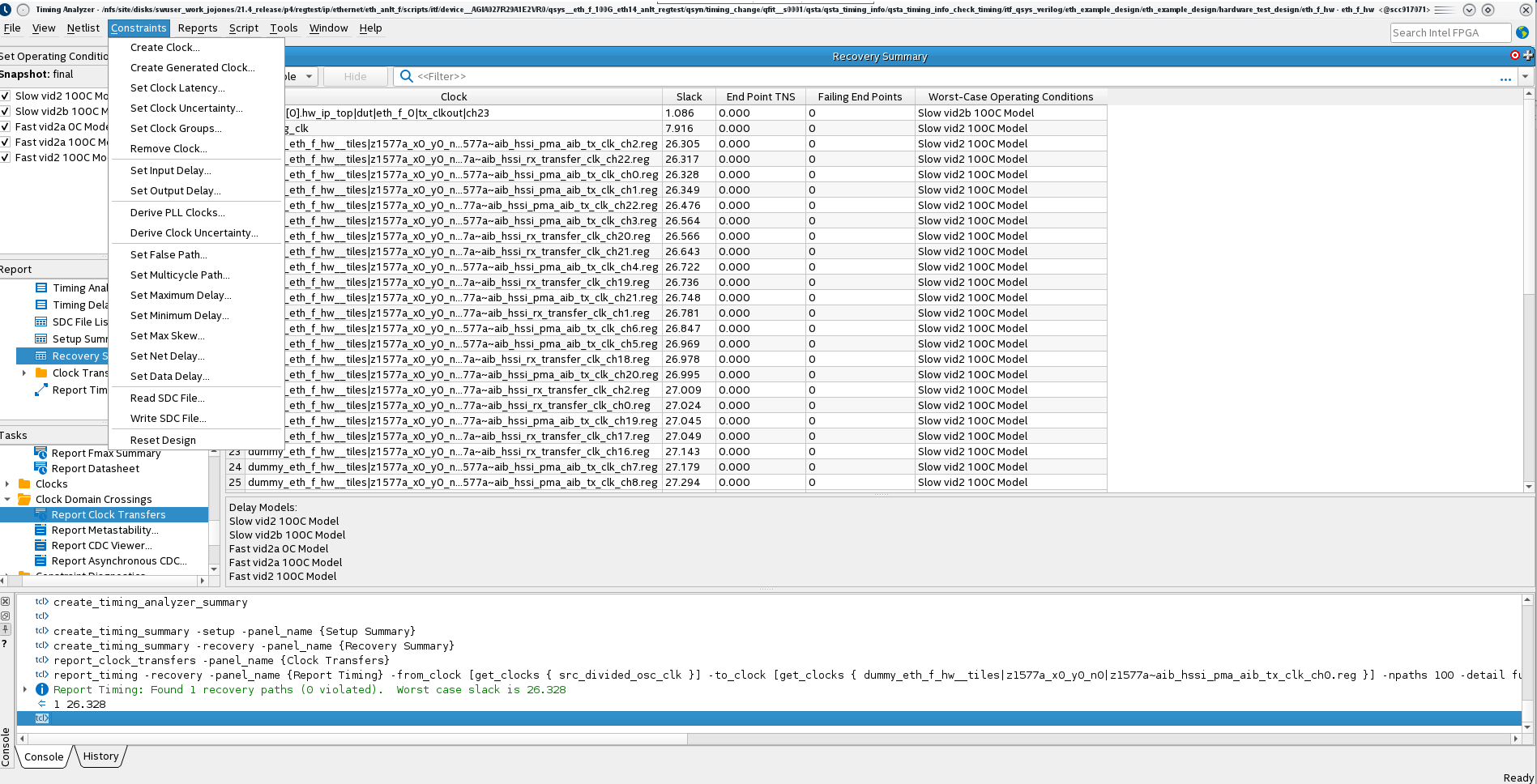

) クロックドメインの交差レポートを 見 て、制約のないタイミングパスを確認します。

これは、制約のないタイミングパスを次のように示します。 非同期 (Timed Unsafe). タイミング・アナライザーがこれらのパスのタイミングエラーを報告しない場合でも、タイミング分析に含めないように制約する必要があります。

これは、制約のないタイミングパスを次のように示します。 非同期 (Timed Unsafe). タイミング・アナライザーがこれらのパスのタイミングエラーを報告しない場合でも、タイミング分析に含めないように制約する必要があります。 -

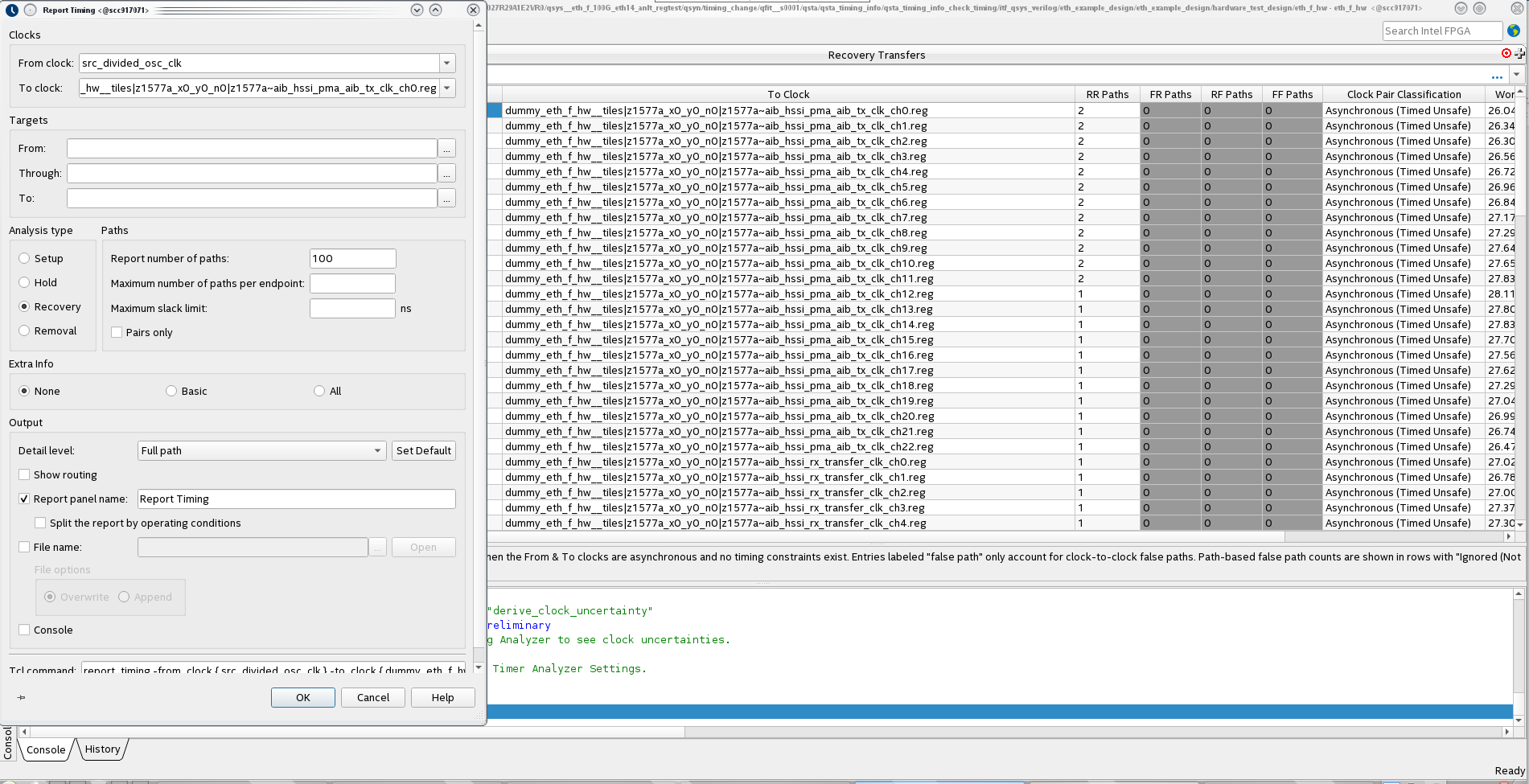

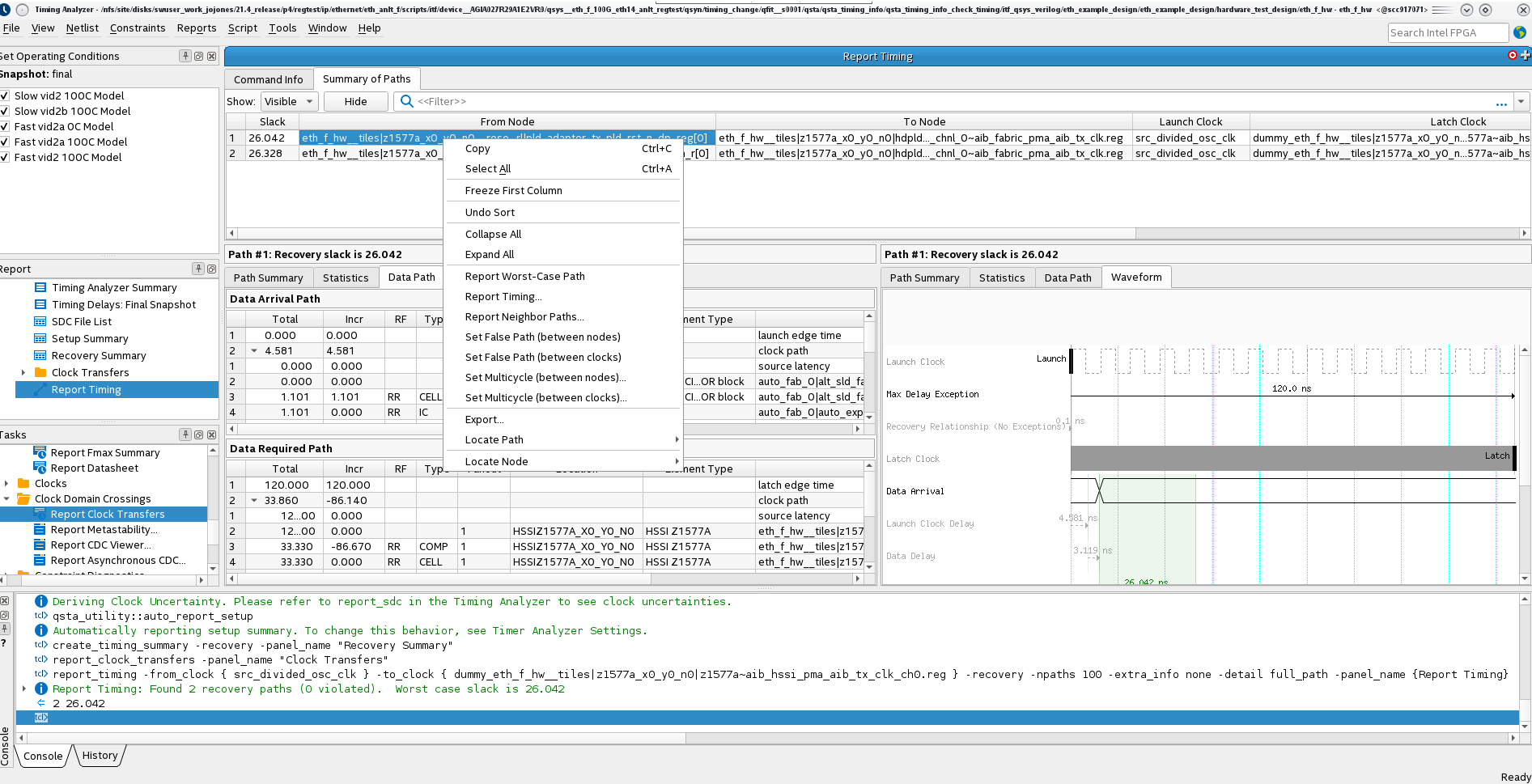

) これらのパスに制約を設定するには、その 1 つを選択し、マウスを右クリックして、[タイミングのレポート] を選択します。表示されているレポートのデフォルトオプションで十分です。

-

) [OK] をクリック します。 タイミングレポートが生成されます。

-

) パスをフォルスパスとして制約するには、タイミング解析に含まれなくなることを意味し、パスの任意の場所を右クリックして、[フォルスパスを設定(ノード間)]....

-

) タイミングレポートを再生成するには、[レポート] ウィンドウに表示されているレポートのいずれかを右クリックして、[すべてを期限切れで再生成] を選択します。

期限切れレポートを再生成した後は、制約したタイミングパスがサマリーレポートに表示されなくなることがわかります。 これは、タイミング・アナライザーがフォルスパスを分析しないように制約しているためです。

期限切れレポートを再生成した後は、制約したタイミングパスがサマリーレポートに表示されなくなることがわかります。 これは、タイミング・アナライザーがフォルスパスを分析しないように制約しているためです。 -

) これを、制約したいすべてのパスで繰り返します。 完了したら、[制約] メニューで [SDC ファイルの書き込み...] を選択して、新しい .sdc ファイルで加えたすべての変更を保存します。

書き込む .sdc ファイルの名前と場所を選択できます。

生成された .sdc ファイルには、デザイン用に最初に読み込んだ .sdc ファイルのすべての制約と、追加した新しい制約が含まれます。

この .sdc ファイルは、将来のコンパイルのために インテル Quartus Prime ソフトウェア・プロジェクトに追加できます。

この問題は、インテル Quartus Prime 開発ソフトウェア・プロ・エディションの今後のリリースで修正される予定です。