インテル Agilex 7 FPGA®汎用 I/O および LVDS SERDES ユーザーガイド のピン配置要件によると、各 x4 DQ グループは同じ OE、リセット、クロック・イネーブル信号を共有しているため、x4 DQ グループ内で OE、リセット、クロックイネーブル信号を分割することはできません。制約がある場合、I2C ピンを配置する際の考慮事項を以下に示します。

1. FPGAは I2C マスターとして使用され、マルチマスター・モードが必要です。

(i) I2C の一般的な実装は、以下に示すように、SCL と SDA の両方に OE を使用しています。したがって、同じ x4 DQ グループに SCL と SDA を配置することはできません。

i2c_serial_scl_inを割り当てる = arduino_adc_scl;

arduino_adc_sclを割り当てる = i2c_serial_scl_oe?1'b0: 1'bz;

i2c_serial_sda_inを割り当てる = arduino_adc_sda;

arduino_adc_sdaを割り当てる = i2c_serial_sda_oe?1'b0: 1'bz;

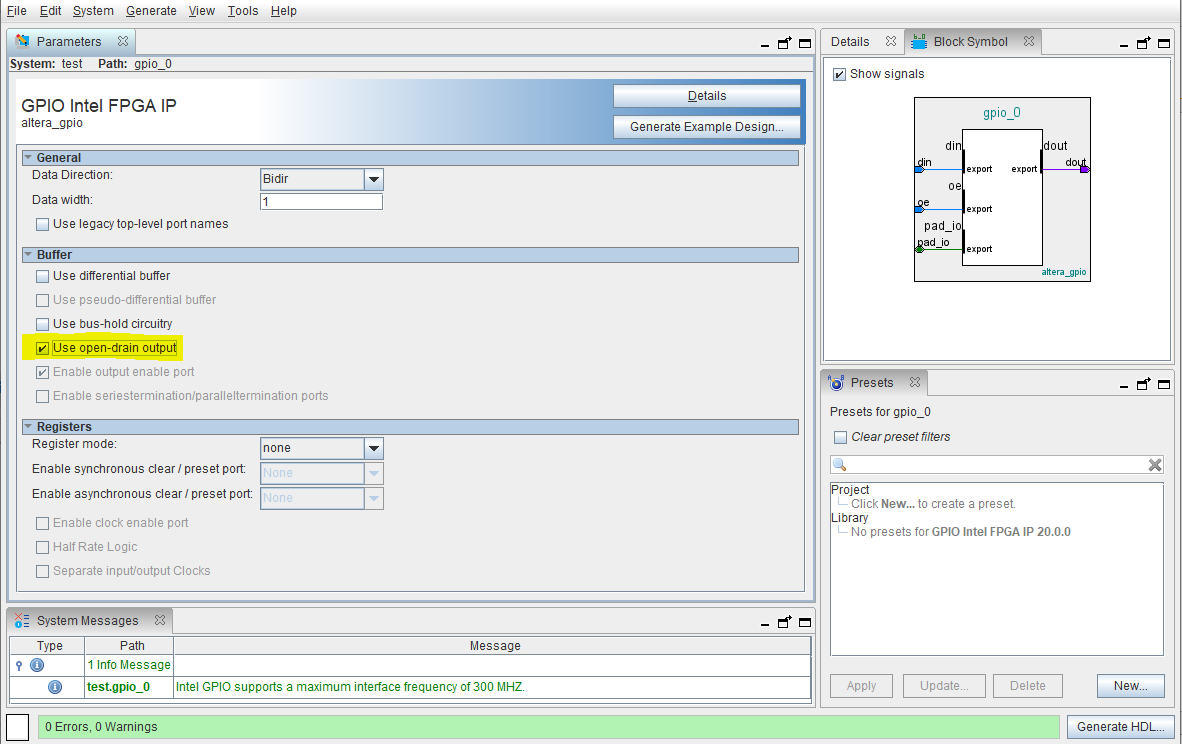

(ii) もう 1 つの方法は、GPIO インテル FPGA IPを使用することです。SCL および SDA のオープンドレインを可能にし、SCL および SDA の両方の OEM ポートを 1 (高) に接続し、元の OE 制御信号の反転信号を接続できます。この方法では、制約を回避できます。以下に例を示します。

gpioip gpioip_scl (

.dout (i2c_serial_scl_in)

.din (~i2c_serial_scl_oe)

.oe (1'b1)

.pad_io (arduino_adc_scl)

);

gpioip gpioip_sda (

.dout (i2c_serial_sda_in)

.din (~i2c_serial_sda_oe)

.oe (1'b1)

.pad_io (arduino_adc_sda)

);

2. FPGAは、I2C マスター・シングルモードとして使用されます。

SCL は、OE がない出力ピンです。SDA は、OE を備えた双方向ピンです。

3. FPGAは I2C スレーブとして使用されます:

SCL は、OE がない入力ピンです。SDA は、OE を備えた双方向ピンです。

上記の 2 と 3 では、SCL には OEM がないため、

- SCL と SDA は、同じ x4 DQ グループ内に割り当てることができます。

- 複数の SCL と SDA を同じ x4 DQ グループに割り当てることができます。

- 同じ x4 DQ グループに複数の SDA を割り当てられない

- 同じ x4 DQ グループに複数の SDA が割り当てられている場合、上記のように GPIO インテル FPGA IPを使用することも回避策です。