バージョン 19.4 以前のバージョンでは、インテル® Stratix® 10 デバイスの Early Power Estimator (EPE) に問題があるため、差動入力ピンを使用してもピンがまだ存在し、すべての I/O バンクの VCCIO 電圧が 2.5V でない場合でも、このエラーが表示されることがあります。

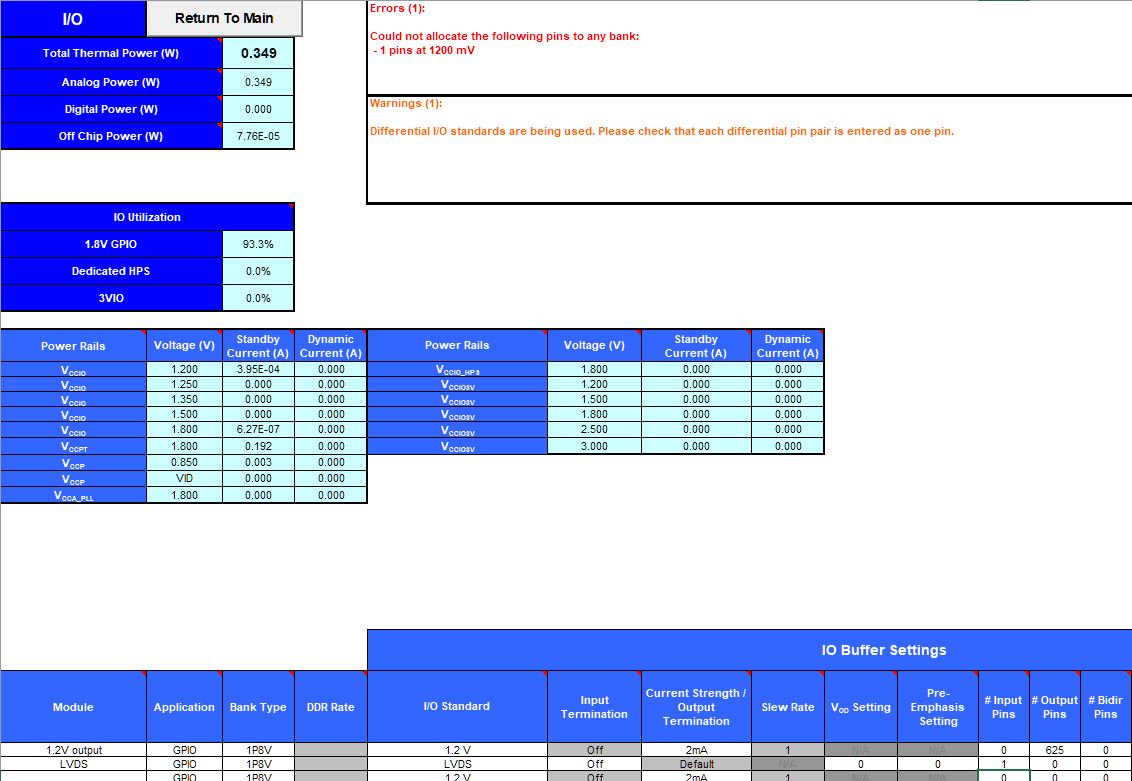

こちらが例です。

- デバイス: 1SG280H

- パッケージ: F50

- ユーザー I/O の数: 672

- I/O バンク数: 14

- プリ I/O バンクのピン数: 48

- ユーザー I/O の用途:

- 1.2 V 出力 * 625 ピン

- LVDS 入力 * 1 ペア

この場合、1.2V 出力に 625 個のピンが使用されるため、14 個の I/O バンクの VCCIO 電圧は 1.2V です。

LVDS 入力は VCCIO ではなく VCCPT によって供給されます。 そのため、2 個の LVDS 入力を残りのピンに割り当てることができます。 しかし、インテル Stratix 10 デバイスの EPE では、次の画像のようなエラーが正しく表示されません。

このエラーは無視しても問題ありません。

この問題は、インテル® Quartus® Prime 開発ソフトウェア・プロ・エディション・バージョン 21.3 の インテル Stratix 10 デバイスの EPE 以降で修正されています。