インテル® Quartus® Prime 開発ソフトウェア・バージョン 19.2 以前のバージョンで問題が発生したため、インテル® Arria® 10 でリモート・システム・アップグレード (RSU) を使用し、10 GX デバイスをインテル Cyclone®した場合、nCONFIG によってトリガーされる再構成では、複数のコンフィグレーション・デバイスが使用され、現在のイメージが2nd または3rdコンフィグレーション・デバイスから設定されている場合、アドレスポインターで指定された初期コンフィグレーション・イメージが読み込まれません。

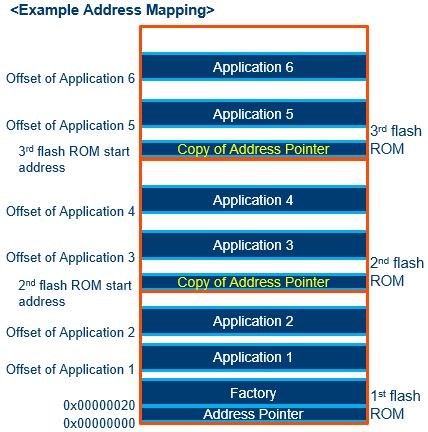

この問題を回避するには、以下のアドレスマッピング例に示すように、アドレスポインターブロックを第 2 および第 3 コンフィグレーション・デバイスの各スタートアドレス (0x0) にコピーする必要があります。

次の手順を使用して .jic ファイルを作成する際には、この回避策を適用できます。

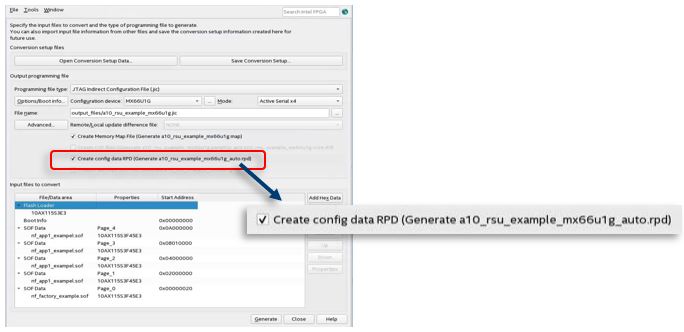

1. プログラミング・ファイル変換ツールを開き、.jic ファイルを生成します。

• コンフィグレーション・データ RPD の作成 (生成された_auto.rpd) オプションを有効にします。

(オプション / 起動情報... > RPD ファイルのビットレベルのエンビアンネス = little endian)

• その他のパラメーターを通常通りに設定する

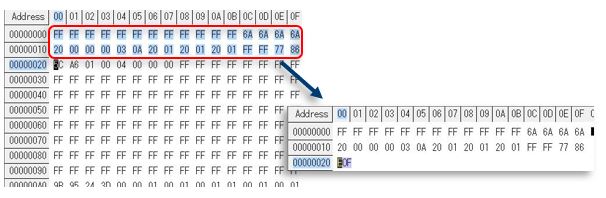

2. バイナリー・ファイル・エディター_flash1_auto.rpd を開きます。

3. 0x0からデータを抽出して0x1Fし、バイナリーファイル (boot_info.bin など) として保存します。

4. コマンドシェルまたは NIOS II コマンドシェルを開き、次のコマンドを実行してバイナリーファイルをsinxファイルに変換します。

nios2-elf-objecopy – I バイナリー –O iシバ<>.bin .分ファイル

元。

nios2-elf-objecopy – I バイナリー –O iシバインboot_info.bin boot_info.boot_info.

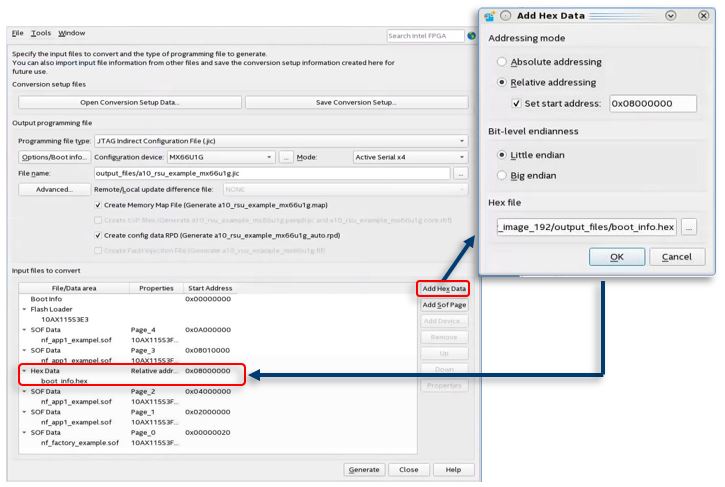

5. プログラミング・ファイルの変換を再度開き、パラメーターとオプションを設定します。

6. [ファイルの追加 ] ボタンをクリックして、メニューの [ファイルの追加] ウィンドウでオプションを設定します。

1) [Addressing Mode]で [相対的アドレス指定] を選択します。

2) スタートアドレスの設定 を有効にして、列に2 番目 のコンフィグレーション・デバイスのスタートアドレスを入力します (例: 2 つの 1G ビット構成デバイスを使用した場合の0x08000000)

3) ビットレベルのエンビアンネスで Little Endian を選択

4) 手順 4 で作成したファイルのファイルを [ファイルの処理 ] 列に指定します。

5) [OK] をクリックします。

3rdコンフィグレーション・デバイスを使用する場合は、手順 6 を繰り返します。

7. [生成 ] をクリックして回避策の .jic ファイルを生成します。

メモ:

• 2 番目または3 番目 のコンフィグレーション・デバイス上のアプリケーション・イメージを更新する場合、アドレス・ポインター・ブロックのコピーを消去しないように、オフセット・アドレスを使用することを推奨します。

たとえば、64KB Erase を使用する場合、アプリケーションイメージには0x10000以上のオフセットアドレスをお勧めします。

• すべてのコンフィグレーション・デバイスのスタートアドレス (0x0) にアドレスポインターブロックが格納されているため、コンフィグレーション・デバイスの境界を越えて画像を保存することはできません。

• アドレスポインターの内容は、コンフィグレーション・デバイスのパーツ番号を変更しない限り変更されません。そのため、ステップ 4 の .jic ファイルを新しいデザインイメージで更新するときに、手順 4 のファイルを再利用できます。

この問題は、インテル Quartus® Prime ソフトウェア・バージョン 20.3 以降修正されています。