JTAG 制約が適切に設定されていないため、複数のタイルにチャネルを持つデザインを読み込む際に、インテル®・トランシーバー・ツールキットで「チャネル TX/RX/LINK|* の設定を取得できない」というエラーが表示されることがあります。ネイティブ PHY ソフトロジックの配置により、異なるタイル上に複数のネイティブ PHY インスタンス化がある場合、問題が最も一般的に発生します。

ソリューションは、ネイティブ PHY のリコンフィグレーション・ポートに供給されるリコンフィグレーション・クロックを制約することです。「altera_reserved_tck」とネイティブ PHY のリコンフィグレーション・クロックポート「rcfg_clk」に接続されたクロックの両方に適切な制約があり、Time Reconfigur 内でタイミングを渡していることを確認します。このクロックは、トランシーバー・ツールキットがトランシーバーの CSR 領域にアクセスするために使用する、Alteraデバッグ Mater Endpoint (ADME) ロジックに使用されます。SDC コマンドの「create_clock」を使用してデザインに宣言されているクロックが 1 つ以上ある場合、自動的に制約されます。JTAG がこのメッセージの出力に自動的に制約を受けているか確認するには、quartus_fitの出力を参照してください。

「JTAG 信号にデフォルトのタイミング制約を追加。 このような制約がユーザーから提供されなかったので、基本的な機能を実現するのに役立ちます。」

あるいは、JTAG クロックをより正確かつ手動で制約したい場合もあります。 これを行うには、Quartus が提供する SDC タイミング・テンプレートを使用します。

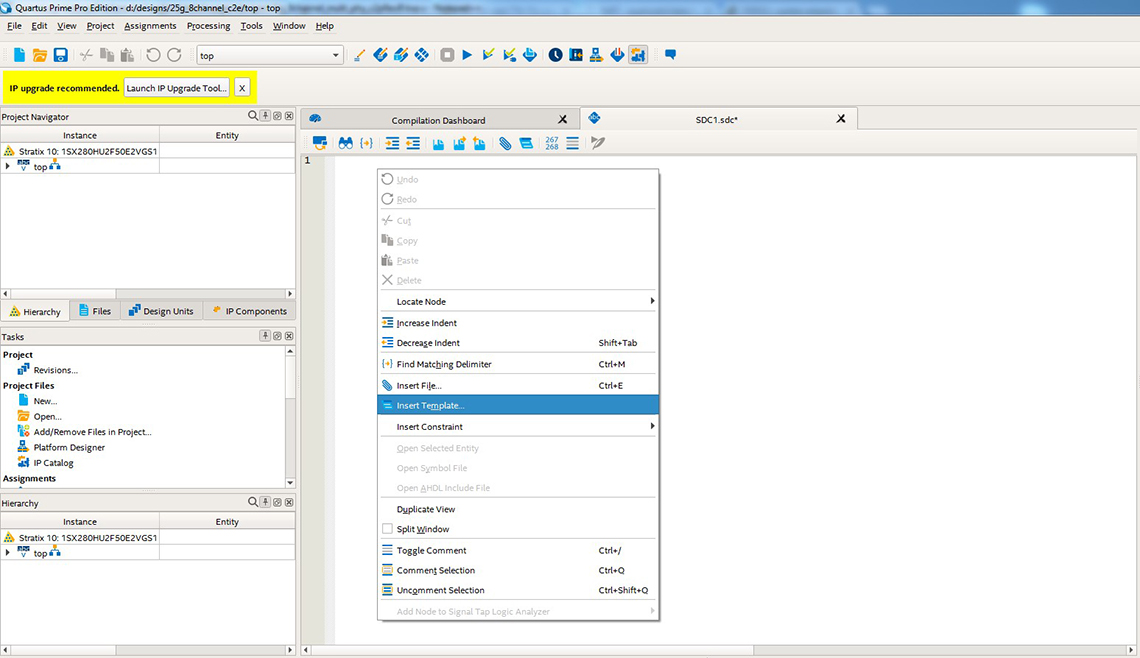

(1) Quartus® Prime 開発ソフトウェア・プロ・エディションで SDC ファイルを開きます (ファイル -> Open)

(2) SDC ファイルウィンドウを右クリックして、ポップアップ・メニューを表示します。

(3) [Insert Kudote] を選択します。

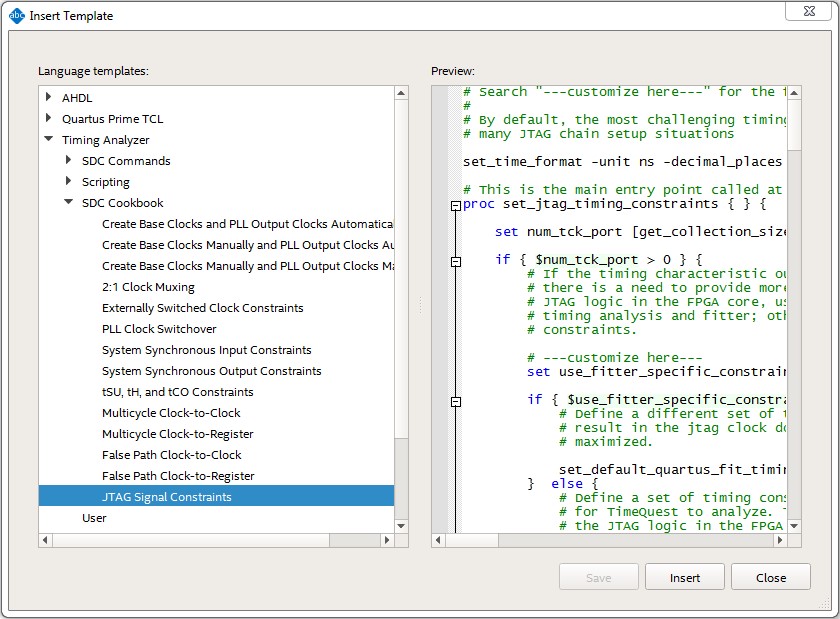

(4) SDC ファイルに制約を挿入するには、「JTAG シグナル制約」を選択します。