プロセスおよびパッケージングによるコンピューティングの再定義

トランジスターとパッケージのイノベーションを通じて次の時代のコンピューティングを推進します。

ムーアの法則における新しいパラダイム

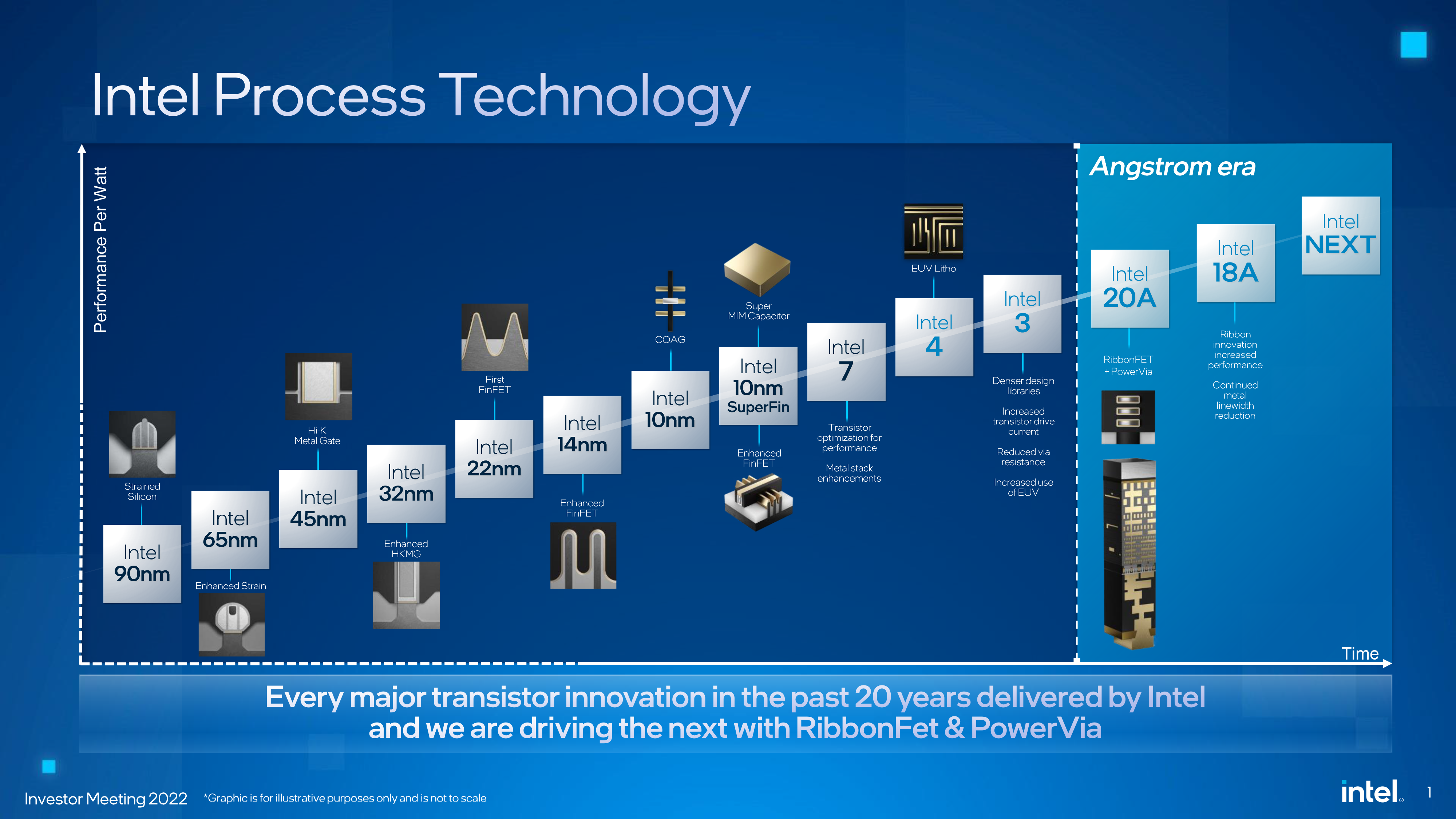

インテルは、ムーアの法則によって PC 時代のコンピューティング・イノベーションのペースを設定しました。データが指数関数的に増加するにつれ、分散したランドスケープ全体でデータを移動、保存、処理するための強力なチップの必要性も増加します。

ムーアの法則はこれまでと同様に重要ですが、目に見える以上のものが存在しているのです。インテルはトランジスター、パッケージング、およびチップ設計の同期化および共同設計された進歩によってデータ中心の時代を支えています。ファブ基盤、社内の研究開発機能、イノベーション・パイプライン、統合デバイスメーカーの優位性など—コンピューティングの可能性を再定義する独自の補完機能を備えた企業は他にありません。

トランジスター: パフォーマンスが飛躍的に向上

マイクロプロセッサーは人間が作った最も複雑な製品であるかもしれません。原子と分子を動かすために細心の注意を払って訓練された熟練専門家によって実行される、世界で最もクリーンな環境での何百ものステップが必要となります。

各マイクロプロセッサーはトランジスターと呼ばれる数十億の小さな電気スイッチにて構成されています。トランジスターが小型化するにつれ、コンピューティング・デバイスはよりスマート、高速、および効率的になります。しかしトランジスターを縮小するだけではパフォーマンスを飛躍的に向上させることはできません。根本的な設計の改善も必要なのです。

3D トランジスターによる小型化と高速化

フィン型電界効果トランジスター (FinFET) の製造を主導するインテルは、2D トランジスターチャネルを 3 次元に引き上げることでチャネルを流れる電子の制御を大幅に改善しました これらのトランジスターは低リークで低電圧にて動作し、パフォーマンスの向上にもかかわらずエネルギー効率を改善するという前例のない組み合わせを実現します。その結果、トランジスターの小型化、高速化、および消費電力の削減がかつてないほど実現しました。約 10 年前の導入以来、インテルは継続的に FinFET の改良を行ってきました。10nm ノードで FinFET トランジスターの 3 度のイテレーション (世代) を実装し、トランジスター・デバイスを超えて金属相互接続、そして最終的にはセルレベルに移行した COAG (Contact Over Active Gate) などの主要なイノベーションでこの技術の改良を続けました。

PowerVia と RibbonFET の導入

FinFET の再定義

インテルは、長年にわたる FinFET プラットフォームの改良を経て、新しい SuperFin テクノロジーにより、前例のないレベルのパフォーマンス向上を実現するようプラットフォームを再定義しました。

SuperFin は、トランジスター・チャネルから最上層の金属層まで、プロセススタック全体にわたるイノベーションの組み合わせを活用しています。画期的なのは、業界標準のアプローチと同じフットプリントで 5 倍の容量増加を実現する新しい Super MIM コンデンサーです。この業界初のテクノロジーにより電圧を下げることができ、これらすべてのイノベーションと組み合わせることで、フルノード移行とほぼ同等のパフォーマンスを実現しました。

イノベーションの加速

今日、インテルはロードマップを新たなレベルのイノベーションを示すものへと進化させ続け、毎年のプロセス改善を可能にするようペースを加速していきます。

新しい Intel 4 および Intel 3 テクノロジーでは、EUV リソグラフィーを全面的に採用しています。これには、13.5nm の波長の光を集束させてシリコン上に非常に小さな形状を印刷する、レンズとミラーの非常に複雑な光学システムが含まれます。これは、193nm の波長の光を使用した以前の技術を大幅に改善したものです。

また、Intel 20A では、PowerVia と RibbonFET という 2 つの新しい画期的なテクノロジーを導入することで、オングストローム時代を先導しています。PowerVia は、インテル独自の、業界初の背面パワーデリバリーの実装です。インテルの GAA (Gate All Around) トランジスター実装となる RibbonFET は、2011年に FinFET を開発して以来、初めて開発した新しいトランジスター・アーキテクチャーです。

名前に込められた意味

インテルは、業界全体のプロセスノードをより正確に把握し、将来のノードの電力効率、パフォーマンス、領域のバランスをより適切に反映するために、プロセス名を新たにしました。何十年もの間、プロセスの「ノード」名は、特定の物理的なトランジスターの実際の長さに一致していました。業界は何年も前にその慣例をやめましたが、ナノメートルなどの寸法単位を連想させる減少する数を使用してノード名を付けるというこの過去のパターンを使い続けてきました。インテルは、お客様が業界全体のプロセスノードをより正確に把握し、より適切な情報に基づいた意思決定を行えるよう、明確で意味のあるフレームワークを作成するために、その表現方法を改めました。

インテルの SuperFIN テクノロジー

パッケージング: 製品イノベーションの促進剤

プロセッサーとマザーボード間の物理インターフェイスとして、チップのパッケージングは製品レベルのパフォーマンスにおいて重要な役割を果たします。高度なパッケージング技術によって多様なコンピューティングエンジンを複数のプロセステクノロジーに統合できるようになり、システムアーキテクチャーのまったく新しいアプローチが可能になります。

組み込みマルチダイ相互接続ブリッジ (EMIB)

当社の Foveros パッケージング・テクノロジーは 3D スタッキングを使用することでロジックオンロジック統合を可能にします。これにより、設計者は新しいデバイスのフォームファクターにおいてテクノロジー IP ブロックをさまざまなメモリーおよび I/O 要素と組み合わせて使用することができます。製品は I/O、SRAM、および電力供給回路がベースダイで製造されると共に高性能ロジックのチップレットやタイルが上部に積み重ねられる小さなチップレットまたはタイルに分割できます。

Foveros による業界初の 3D スタッキング

当社の Foveros パッケージング・テクノロジーは 3D スタッキングを使用することでロジックオンロジック統合を可能にします。これにより、設計者は新しいデバイスのフォームファクターにおいてテクノロジー IP ブロックをさまざまなメモリーおよび I/O 要素と組み合わせて使用することができます。製品は I/O、SRAM、および電力供給回路がベースダイで製造されると共に高性能ロジックのチップレットやタイルが上部に積み重ねられる小さなチップレットまたはタイルに分割できます。

次世代パッケージング

インテルの最新パッケージング能力はお客様の設計を新たな世界へと導きます。インテルの EMIB テクノロジーと Foveros テクノロジーを組み合わせると、基本的にシングルチップのパフォーマンスでさまざまなチップレットとタイルを相互接続できます。Foveros Omni により、設計者はパッケージ内のチップレットやタイル間の通信をより柔軟に行うことができます。

統合された利点

垂直統合型デバイスメーカー (IDM) として、インテルは強力なコンピューティング・エンジンおよびリーダーシップ・パッケージを組み合わせることで比類のない製品統合を実現しています。弊社の補完的な機能であれば設計、プロセス、パッケージングをクラス最高の製品に完全に統合できます。また CPU、FPGA、アクセラレーター、およびグラフィックス処理チップのポートフォリオにより、設計者は製品に最適なトランジスターを選択するための最高の柔軟性を備えています。

業界初のハイブリッド・アーキテクチャー

コード名「Lakefield」と呼ばれるインテル独自のプロセッサーは、ハイブリッド CPU と Foveros 3D パッケージングテクノロジーを組み合わせています。このアーキテクチャーは設計、フォームファクター、およびエクスペリエンスを革新するための柔軟性を提供します。

トランジスターは何年も何十年もかけて進化し、私たちが利用するすべてのコンピューティングの基礎となりました。この驚くべき見た目の変化において、この重要な発明にどれだけのイノベーションが生まれたか、そしてそれらにはまだ発展の余地があるということをインテルは示しています。

通知と免責条項

インテルのプロセス・テクノロジー・イノベーションの詳細については、www.intel.com/ProcessInnovation を参照してください。

すべての製品およびサービスプラン、ロードマップ、性能予測は、予告なく変更されることがあります。将来のノード・パフォーマンスやその他の指標に関する予測は、本質的に不確実です。

このドキュメントには、プロセスおよびパッケージング・テクノロジーのロードマップを含む、インテルの将来のプランや予想など未来の見通しに関する記述が含まれています。これらの記述は現在の予想に基づいており、実際の結果がそのような記述で表明または暗示されたものと大きく異なる原因となる可能性のある多くのリスクと不確実性を伴います。実際の結果が大幅に異なる可能性のある要因の詳細については、www.intc.com の最新の収益リリースおよび SEC 提出書類を参照してください。

インテル® テクノロジーの機能および利点はシステム構成によって異なり、対応するハードウェアやソフトウェア、またはサービスの有効化が必要となる場合があります。実際の性能はシステム構成によって異なります。絶対的なセキュリティーを提供できる製品またはコンポーネントはありません。詳細については、各システムメーカーまたは販売店にお問い合わせいただくか intel.co.jp を参照してください。

ここで提供されるすべての情報は予告なしに変更される場合があります。