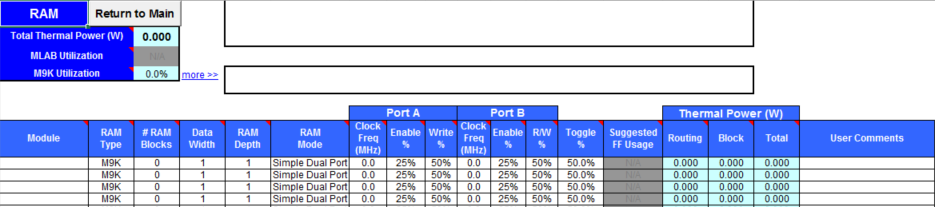

3.3. Cyclone® 10 LP EPE - RAM ワークシート

Early Power Estimator (EPE) スプレッドシートの RAM ワークシートの各行は、同じ RAM ブロックのタイプ、同じデータ幅、同じ RAM の深さ ( 該当する場合 )、同じ RAM モード、および同じポート・パラメーターのデザインモジュールを表します。デザインの一部、もしくはすべての RAM ブロックが異なるコンフィグレーションを有する場合、異なる行に情報を入力します。各デザインモジュールで、実装された RAM タイプ、RAM ブロック数、RAM ブロックモードを入力します。

また、EPE スプレッドシートの RAM ワークシートの各行は、複数の RAM ブロックに物理的に実装できる論理 RAM モジュールを表しています。EPE スプレッドシートは、入力された論理幅と深さに基づいて、可能な限り電力効率に優れた方法で、最少の物理 RAM ブロック数を用いて各論理 RAM モジュールを実装します。

RAM ブロックモードを選択する際は、 Quartus® Prime Compiler での RAM の実装方法を把握していなければなりません。例えば、ROM が2つのポートで実装されている場合、ROM ではなく、ト ゥルー・デュアルポート・メモリーと見なされます。シングルポートと ROM の実装では、ポート A のみを使用します。シンプル・デュアルポートとトゥルー・デュアルポートの実装では、ポ ート A とポート B を使用します。

| カラムヘッダー | 説明 |

|---|---|

| Module | RAM モジュール名を入力します ( オプション値 )。 |

| RAM Type | 実装される RAM タイプを選択します。 RAM タイプは、 Quartus® Prime Compilation Report の Type 列で確認することができます。Compilation ReportでFitterとResource Sectionを選択します。RAM Summaryをクリックします。 |

| #RAM Blocks |

同じタイプとモードを使用し、各ポートで同じパラメーターを有するモジュールの RAM ブロック数を入力します。各ポートのパラメーターは、次の通りです。

RAMブロック数は、 Quartus® PrimeCompilation Report の MLAB または M9K の列で確認できます。Compilation ReportでFitterを選択し、Resource Sectionをクリックします。RAM Summaryをクリックします。 |

| Data Width | RAM ブロックのデータ幅を入力します。この値は、RAM タイプに基づいて制限されています。RAM ブロックの幅は、 Quartus® Prime Compilation Report の Port A Width または Port B Width 列で確認できます。Compilation ReportでFitterを選択し、Resource Sectionをクリックします。RAM Summaryをクリックします。 ポート A とポート B でデータ幅が異なる RAM ブロックでは、大きい方のデータ幅を使用します。 |

| RAM Depth | RAM ブロックの深さを単語数で入力します。 RAM ブロックの深さは、 Quartus® Prime Compilation Report の Port A Depth または Port B Depth 列で確認できます。Compilation ReportでFitterを選択し、Resource Sectionをクリックします。RAM Summaryをクリックします。 |

| RAM Mode |

以下のモードから選択します。

モードは、 Quartus® Prime Compiler での RAM の実装方法に基づきます。メモリーモジュールの実装方法が不明な場合、 インテル® は Quartus® Prime ソフトウェアでの必要なコンフィグレーションを使用したテストケースのコンパイルを推奨しています。RAM モードは、 Quartus® Prime Compilation Report の Mode 列で確認できます。Compilation ReportでFitterを選択し、Resource Sectionをクリックします。RAM Summaryをクリックします。 シングルポート RAM は、1つのポートにリードとライトの制御信号を有します。シンプル・デュアルポート RAM は、リードとライトのポートを1つずつ有します。トゥルー・デュアルポート RAM はポートを2つ有し、それぞれにリードとライトの制御信号があります。 ROM は、リード専用のシングルポート RAM です。 |

| Port A–Clock Freq (MHz) | RAM データおよびアドレス入力の動作に関係なく、ポート A の入力クロックイネーブルがアクティブな時間の平均割合を入力します。イネーブルの割合は、0~100%です。デフォルト値は25%です。 RAM の電力は、主にクロックイベントの発生時に消費されます。リードまたはライト動作が発生していない場合、クロックイネーブル信号を使用してポートをディスエーブルすると、消費電力を大幅に節約できます。 |

| Port A–Enable % | RAM データおよびアドレス入力での動作に関係なく、ポート A の入力クロックイネーブルがアクティブな時間の平均割合を入力します。イネーブルの割合は、0~100%です。 RAM の電力は、主にクロックイベントの発生時に消費されます。リードまたはライト動作が発生しない場合、クロックイネーブル信号を使用してポートをディスエーブルすると、消費電力を大幅に節約できます。 |

| Port A–Write % | RAM ブロックのポート A がライトモードとリードモードでの時間の平均割合を入力します。シンプル・デュアルポート (1R / 1W) RAM では、ライト動作を実行していない場合はライトポート A は非アクティブです。シングルポートおよびデュアルポート RAM では、ポート A がライトされていない時にリードします。このフィールドは ROM モードの RAM では無視されます。 この値は、0~100%でなければなりません。デフォルト値は50%です。 |

| Port B–Clock Freq (MHz) | RAM ブロックのポート B のクロック周波数を単位 MHz で入力します。この値は、RAM タイプとデバイスファミリーのより大きい周波数仕様により、制限されています。ポート B は、ROM、シングルポート・モード、または選択された RAM タイプが MLAB の場合は RAM ブロックでは無視されます。 |

| Port B–Enable % | RAM データおよびアドレス入力での動作に関係なく、ポート B の入力クロックイネーブルがアクティブな時間の平均割合を入力します。イネーブルの割合は、0~100%です。 RAM の電力は、主にクロックイベントの発生時に消費されます。リードまたはライト動作が発生しない場合、クロックイネーブル信号を使用してポートをディスエーブルすると、消費電力を大幅に節約できます。 |

| Port B–R/W % | トゥルー・デュアルポート・モードの RAM ブロックの場合、RAM ブロックのポート B がライトモードとリードモードになる時間の平均割合を入力します。シンプル・デュアルポート・モードの RAM ブロックの場合、RAM ブロックのポート B のリード時間の割合を入力します。シンプル・デュアルポート・モードでは、ポート B にライトできません。ポート B は、ROM、シングルポート・モード、または選択された RAM タイプが MLAB の場合は RAM ブロックでは無視されます。 この値は、0~100%でなければなりません。デフォルト値は50%です。 |

| Toggle% | クロックサイクルごとに各ブロック出力信号が値を変える頻度の平均割合は、クロック周波数とイネーブルの割合で乗算され、1秒あたりの遷移数が算出されます。この値は配線消費電力にのみ影響を及ぼします。 50% はランダムに変化する信号に相当します。ランダム信号は時間の半分のみ状態を変化させます。 |

| Suggested FF Usage | 正確な MLAB 機能のために必要な FF ( フリップフロップ ) の数を表示します。RAM ワークシートの MLAB の消費電力には、FF の消費電力は含まれません。 デバイスリソースを手動で入力する場合、同じクロック周波数を使用する Logic ワークシートに推奨される FF 数を加えます。 EPE ファイルからデバイスリソースをインポートしている場合は、何もする必要はありません。 このフィールドは、選択した RAM タイプが MLAB の場合にのみ有効です。 |

| Thermal Power (W)–Routing | 配線見積りによる消費電力を単位 W で示します。 配線消費電力は、配置配線によって異なり、デザインの複雑さに関係します。ここに示された値は、100 以上のデザインの観測に基づいた配線消費電力を表しています。 デザインの配線に基づく解析の詳細については、 Quartus® Prime Power Analyzer を使用します。この値は自動的に計算されます。 |

| Thermal Power (W)–Block | RAM の内部トグルに起因する消費電力を単位 W で示します。 デザインの正しい RAM モードに基づくより正確な解析は、 Quartus® PrimePower Analyzer を使用します。この値は自動的に計算されます。 |

| Thermal Power (W)–Total | 入力情報に基づいて見積られた消費電力を単位 W で示します。RAMブロックでの総消費電力で、配線消費電力とブロック消費電力の合計と同じです。この値は自動的に計算されます。 |

| User Comments | コメントを入力します(オプション入力)。 |

RAM ブロックのコンフィグレーションについて詳しくは、Cyclone® 10 LP Device Handbook のMemory Blocksの項を参照してください。