インテルのみ表示可能 — GUID: drh1576733802322

Ixiasoft

1.3.1.1. インテルAgilexデュアルリンクへの同期ADC用のデザイン例プラットフォーム・デザイナーシステムの編集

1.3.1.2. インテルAgilexデュアルリンクへの同期ADC用のデザイン例トップレベルのHDLの編集

1.3.1.3. インテルAgilexデュアルリンクへの同期ADC用のTXシミュレーション・モデルプラットフォーム・デザイナーシステムの編集

1.3.1.4. インテルAgilexデュアルリンクへの同期ADC用のTXシミュレーション・モデルのトップレベルのHDLの編集

1.3.1.5. インテルAgilexデュアルリンクへの同期ADC用のシミュレーション・テストベンチの編集

1.3.1.6. シミュレーション波形へのIP信号の追加

1.3.1.7. シミュレーション・スクリプトの更新

1.3.1.8. デュアル・リンク・デザインのシミュレーション

1.3.1.9. シミュレーション結果の表示

インテルのみ表示可能 — GUID: drh1576733802322

Ixiasoft

1.3.1.9. シミュレーション結果の表示

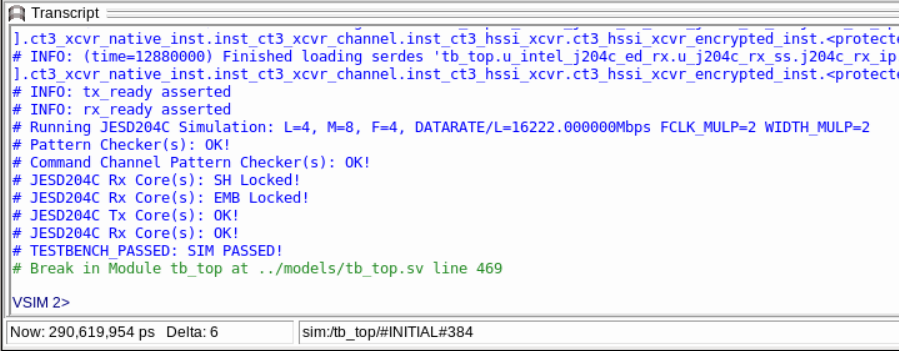

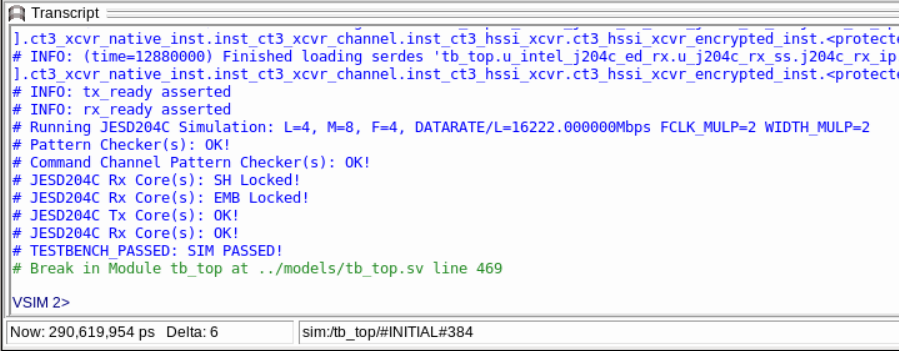

シミュレーション・テストベンチは、シミュレーション・スクリプトを実行するトランスクリプトまたはターミナルに結果を出力します。 次の例は、ModelSim- Intel® FPGA Editionでのシミュレーションの出力および波形を示しています。

シミュレーションに合格すると、次の図に示すとおり、トランスクリプト・セクションに TESTBENCH_PASSED: SIM PASSED! が出力されます。

図 11. ModelSim‐ Intel® FPGA Editionのシミュレーション結果のトランスクリプト

シミュレーションに失敗した場合、失敗の理由と一緒に、トランスクリプト・セクションに TESTBENCH_FAILED: SIM FAILED! が出力されます。

波形を表示する場合、リンクの初期化中に次のイベントが発生します。

- /tb_top/ninit_done とグローバルリセットがデアサートされた後、リセット・シーケンサーは、JESD204C Intel FPGA IPのLink 0とLink 1の両方でTXおよびRXトランシーバーのリセットをデアサートします。

- /tb_top/tx_ready は、Link 0および1のTXトランシーバー・チャネルの準備ができるとアサートされます。

- TX JESD204C IPのリンクリセット /tb_top/tx_rst_n は、コアIO PLLがロックされ、intel_jesd204c/tx_pma_ready および intel_jesd204c/tx_ready がアサートされると、デアサートされます。

- TXチャネルがRXチャネルにデータを送信する場合、RXトランシーバー・チャネルのReady信号 /tb_top/rx_ready はアサートされません。RX JESD204C IPのリンクリセット /tb_top/rx_rst_n がアサートされます。

図 12. グローバル・リセット・デアサート後のModelSim‐ Intel® FPGA Editionシミュレーション波形

- RXトランシーバー・チャネルがデータとクロックを正常に回復すると、/tb_top/rx_ready がアサートされます。

- RX JESD204C IPのリンクリセット /tb_top/rx_rst_n は、コアIO PLLがロックされ、intel_jesd204c/rx_pma_ready および intel_jesd204c/rx_ready がアサートされると、デアサートされます。

図 13. RXトランシーバー・チャネルがReadyの場合のModelSim‐ Intel® FPGA Editionシミュレーション波形

- /tb_top/rx_rst_n がデアサートされると、RXトランスポート層はリセットされなくなります。RXトランスポート層は、j204c_rx_avst_ready 信号をJESD204C Intel FPGA IPにアサートします。

- RX JESD204C IPは、64個の連続した有効な同期ヘッダーが検出されると、同期ヘッダーのアライメントを実現します (j204c_rx_sh_lock がアサートされます)。

- RX JESD204C IPは、4つの連続した有効なシーケンスが検出されると、拡張マルチブロック・アライメントを実現します (j204c_rx_emb_lock がアサートされます)。有効なシーケンスは、完全なE*32ビット同期遷移ストリームの正しいEoEMBおよびEoMB値として定義されます。

- j204c_rx_alldev_lane_align は、両方のRX JESD204C IPがレーン・アライメントを達成するとアサートされます。

- j204c_rx_avst_valid は、RXトランスポート層がユーザーデータをstart-of-multiblock (j204c_rx_somb) およびstart-of-extended-multiblock (j204c_rx_soemb) マーカーとともにアプリケーション・レイヤーにストリーミングするときにアサートされます。

- RX JESD204C IPのコマンドチャネルは、CRC-12信号を同期ヘッダーストリームに出力します。CRCエラー (j204c_rx_crc_err) は検出されません。コマンドチャネルでパリティーエラー (j204c_rx_cmd_par_err) は検出されません。

図 14. リンクの初期化に成功したModelSim‐ Intel® FPGA Editionシミュレーション波形図 15. データエラーなしのModelSim‐ Intel® FPGA Editionシミュレーション波形

- パターンチェッカーは、RXトランスポート層から受信したサンプルデータをチェックします。エラー (/tb_top/data_error) は検出されません。

- パターンチェッカーは、RX JESD204C IPから受信した同期ヘッダーをチェックします。エラー (/tb_top/cmd_data_error) は検出されません。

- TXとRXリンクエラーまたは割り込み (/tb_top/tx_link_error および /tb_top/rx_link_error) は、TXとRX JESD204C IPの両方によってアサートされていません。テストベンチは、test_passed フラグをアサートします。