インテルのみ表示可能 — GUID: mtr1430270862294

Ixiasoft

インテルのみ表示可能 — GUID: mtr1430270862294

Ixiasoft

2.4.2.6. リードモディファイライトメモリー

インテル® Hyperflex™ M20Kメモリー・ブロックは、コヒーレント・リードをサポートし、リード・モディファイ・ライト・メモリーの実装を簡素化します。リード・モディファイ・ライトのメモリーは、ネットワーク統計カウンターなどのアプリケーションで役立ちます。リード・モディファイ・ライト・メモリーは、1サイクルでインクリメントとリライティングを必要とするメモリーに値を格納するアプリケーションでも役に立ちます。

M20Kメモリーブロックは、手書きキャッシング回路の必要性を排除して実装を簡素化します。高いクロックレートまたは大きなカウンターのために、複数のクロックサイクルにわたって修正動作をパイプライン化しなければならないキャッシング回路は複雑になります。

コヒーレントのリード機能を使用するには、出力データポートをレジスターするかどうかに応じてメモリーを接続します。出力データポートをレジスターする場合、メモリーをインスタンス化するときに、ライト・イネーブル・ラインおよびライト・アドレス・ラインに2つのレジスターステージを追加します。

出力データポートをレジスターしない場合、メモリーをインスタンス化する際に、ライト・イネーブル・ラインおよびライト・アドレス・ラインに1つのレジスターステージを追加します。

コヒーレント・リードの使用には次の制限があります。

- リードとライトに同じクロックを使用する必要があります。

- リード・ポートおよびライト・ポートには同じ幅を使用する必要があります。

- ECCは使用できません。

- バイトイネーブルを使用できません。

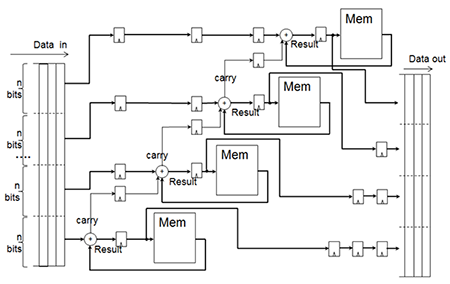

図 69は、最近のアクティビティを追跡するためのキャッシュを維持せずに、パフォーマンスを改善する読み取り-変更-書き込みメモリーのパイプライン化方法を示しています。

コヒーレント読み取りと互換性のないM20Kメモリー機能が必要な場合、またはコヒーレント・リードを使用したくない場合、次の代替アプローチを使用してメモリーのfMAXパフォーマンスを改善します。

- 変更操作を1つのクロックサイクルで完了することができる小さなブロックに分割します。

- 各チャンクが1つのM20Kメモリーブロックよりも広くないことを確認してください。コンパイラーは、データワードを複数のnビットチャンクに分割します。各チャンクは、1クロックサイクルで効率的に処理するのに十分な小ささです。

- fMAXを増やすには、メモリーブロックの数を増やし、狭いメモリーブロックを使用して、レイテンシーを増やします。レイテンシーを減らすには、使用するメモリーブロックを減らして広くし、パイプライン・ステージを適切に削除します。 read-modify-write回路のループは、回路の性質上避けられませんが、このソリューションのループは小さくて短いです。基になる構造はパイプライン・ステージの数に関係なく同じままであるため、このソリューションはスケーラブルです。