インテルのみ表示可能 — GUID: lfb1468436589960

Ixiasoft

2.4.2.1. 高速クロック・ドメイン

2.4.2.2. ループの再構築

2.4.2.3. コントロール信号のバックプレッシャー

2.4.2.4. FIFOステータス信号によるフロー・コントロール

2.4.2.5. スキッドバッファーを使用したフロー制御

2.4.2.6. リードモディファイライトメモリー

2.4.2.7. カウンターとアキュムレーター

2.4.2.8. ステートマシン

2.4.2.9. メモリー

2.4.2.10. DSPブロック

2.4.2.11. 一般ロジック

2.4.2.12. モジュラスと除算

2.4.2.13. リセット

2.4.2.14. ハードウェアの再利用

2.4.2.15. アルゴリズム要件

2.4.2.16. FIFO

2.4.2.17. 三進加算器

インテルのみ表示可能 — GUID: lfb1468436589960

Ixiasoft

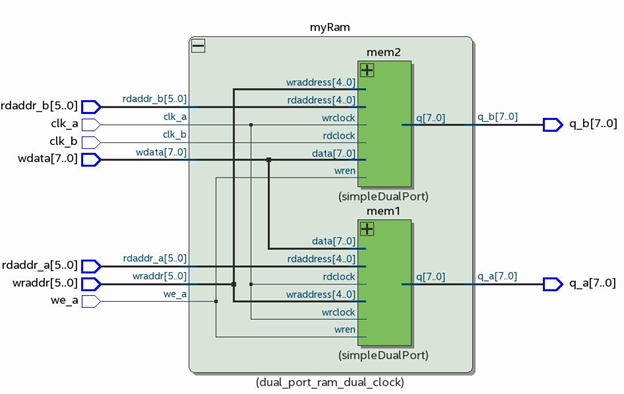

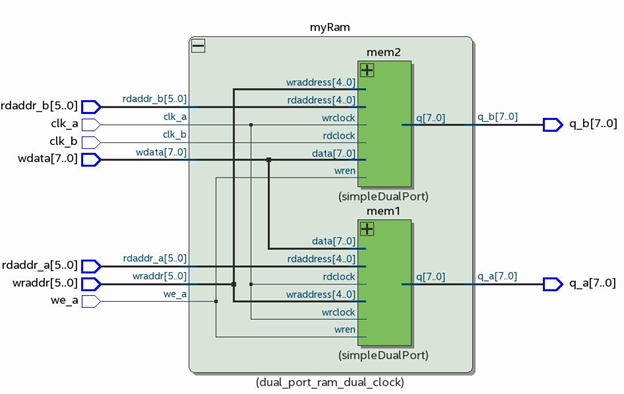

2.4.2.9.3. インテル® Hyperflex™ アーキテクチャーのシンプル・デュアル・ポート・メモリーの例

2つのシンプル・デュアル・ポート・メモリーを使用すると、デバイスのM20Kブロックを2倍にすることができます。しかしながら、このメモリー構造は1GHzまでの周波数で実行することができます。 インテル® Hyperflex™ デバイスで独立したクロックを持つ真のデュアル・ポート・メモリーを使用している場合、この周波数は不可能です。

図 73. シンプル・デュアル・ポート・メモリーのコンフィグレーション

GUIのインスタンス化ではなく、単純なデュアル・ポート・メモリーをRTLで推測することで、同様の周波数結果を得ることができます。

シンプル・デュアル・ポートRAM

module simple_dual_port_ram_with_SDPs

#(parameter DATA_WIDTH=8, parameter ADDR_WIDTH=6)

(

input [(DATA_WIDTH-1):0] wrdata,

input [(ADDR_WIDTH-1):0] wraddr, rdaddr,

input we_a, wrclock, rdclock,

output reg [(DATA_WIDTH-1):0] q_a

);

// Declare the RAM variable

reg [DATA_WIDTH-1:0] ram[2**ADDR_WIDTH-1:0];

always @ (posedge wrclock)

begin

// Port A is for writing only

if (we_a)

begin

ram[wraddr] <= wrdata;

end

end

always @ (posedge rdclock)

begin

// Port B is for reading only

begin

q_a <= ram[rdaddr];

end

end

endmoduleトゥルー・デュアル・ポートRAMの動作エミュレーション

module test (wrdata, wraddr, rdaddr_a, rdaddr_b,

clk_a, clk_b, we_a, q_a, q_b);

input [7:0] wrdata;

input clk_a, clk_b, we_a;

input [5:0] wraddr, rdaddr_a, rdaddr_b;

output [7:0] q_a, q_b;

simple_dual_port_ram_with_SDPs myRam1 (

.wrdata(wrdata),

.wraddr(wraddr),

.rdaddr(rdaddr_a),

.we_a(we_a),

.wrclock(clk_a), .rdclock(clk_b),

.q_a(q_a)

);

simple_dual_port_ram_with_SDPs myRam2 (

.wrdata(wrdata),

.wraddr(wraddr),

.rdaddr(rdaddr_b),

.we_a(we_a),

.wrclock(clk_a), .rdclock(clk_a),

.q_a(q_b)

);

endmodule